Máy Tính

Bài tập kiến trúc máy tính: Tổng hợp và lời giải chi tiết

Kiến trúc máy tính là một trong những nền tảng cốt lõi của ngành công nghệ thông tin, giúp chúng ta hiểu cách các hệ thống máy tính hoạt động ở cấp độ phần cứng. Việc nắm vững kiến thức này đòi hỏi không chỉ lý thuyết mà còn cần thực hành giải các dạng bài tập đa dạng. Bài viết này từ lavender-panther-755911.hostingersite.com cung cấp bộ sưu tập bài tập kiến trúc máy tính có lời giải chi tiết, bao gồm các dạng từ cơ bản đến nâng cao, trải dài qua nhiều chương khác nhau, giúp sinh viên và những người đam mê công nghệ củng cố kiến thức, nâng cao kỹ năng giải quyết vấn đề. Đây là tài liệu hữu ích dành cho những ai đang tìm kiếm nguồn ôn tập toàn diện và đáng tin cậy.

Giới thiệu tổng quan về Kiến trúc Máy tính và Tầm quan trọng của bài tập thực hành

Kiến trúc máy tính là lĩnh vực nghiên cứu về cách một hệ thống máy tính được thiết kế và vận hành. Nó bao gồm việc tìm hiểu về cấu trúc của CPU, bộ nhớ, các thiết bị ngoại vi và cách chúng tương tác với nhau để thực hiện các tác vụ. Từ các lệnh máy cơ bản đến quản lý bộ nhớ phức tạp, mọi thành phần đều đóng vai trò quan trọng trong hiệu suất và chức năng tổng thể của máy tính. Việc hiểu rõ kiến trúc này không chỉ là nền tảng cho lập trình viên mà còn cho các kỹ sư phần cứng và chuyên gia mạng.

Tầm quan trọng của việc giải bài tập kiến trúc máy tính không thể phủ nhận. Lý thuyết suông thường khó hình dung và áp dụng vào thực tế. Bài tập giúp biến kiến thức trừu tượng thành kỹ năng cụ thể, cho phép người học:

- Củng cố lý thuyết: Áp dụng các khái niệm đã học vào các tình huống cụ thể, từ đó hiểu sâu hơn về chúng.

- Phát triển tư duy logic: Rèn luyện khả năng phân tích vấn đề và tìm ra giải pháp tối ưu.

- Nâng cao kỹ năng giải quyết vấn đề: Đối mặt với các thách thức thực tế trong thiết kế và vận hành hệ thống.

- Chuẩn bị tốt cho thi cử: Làm quen với các dạng câu hỏi và cải thiện tốc độ xử lý.

Thông qua việc thực hành các bài tập kiến trúc máy tính với lời giải chi tiết, người học sẽ có cái nhìn toàn diện hơn về cách các thành phần máy tính hoạt động và tương tác, từ đó xây dựng được nền tảng vững chắc cho sự nghiệp trong ngành công nghệ thông tin.

Bài tập kiến trúc máy tính cơ bản

Xem Thêm Bài Viết:

- Cách Tăng Tốc Máy Tính Win 8 Hiệu Quả Nhất Hiện Nay

- Máy in Canon Pixma G3010: Đánh giá chi tiết

- Kích thước Tem Nhãn Phù Hợp Máy In Brother QL-700/800

- Mua Máy Tính Cũ Uy Tín Hà Nội: Hướng Dẫn Toàn Diện

- Hướng Dẫn Chi Tiết Đổi Pass WiFi FPT Bằng Máy Tính

Hướng dẫn giải các dạng bài tập Kiến trúc Máy tính cơ bản

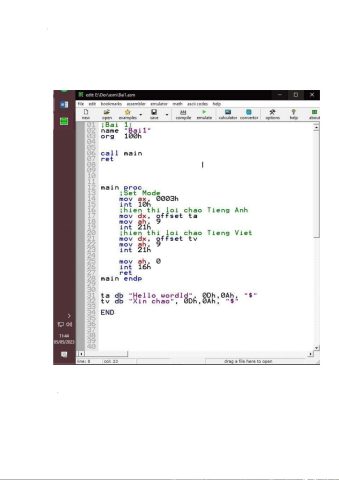

Để giúp bạn dễ dàng tiếp cận và nắm vững các kiến thức cơ bản về kiến trúc máy tính, chúng tôi sẽ đi sâu vào giải thích các dạng bài tập điển hình. Mỗi bài tập sẽ được trình bày với lời giải thích từng bước, cụ thể, nhằm làm rõ nguyên lý hoạt động của các lệnh và thành phần máy tính.

Bài tập về Cấu trúc Lệnh và Thanh ghi

Trong phần này, chúng ta sẽ xem xét các bài tập liên quan đến cấu trúc lệnh máy 8-bit, địa chỉ 5-bit, cùng với các thao tác cơ bản như LOAD, STORE và ADD. Các lệnh này minh họa cách CPU tương tác với bộ nhớ và các thanh ghi để xử lý dữ liệu.

Bài 1: XÉT MỘT MÁY TÍNH VỚI TẬP LỆNH MÁY KHUÔN DẠNG 8-BIT, VỚI PHẦN ĐỊA CHỈ CHỈ CÓ MỘT THÀNH PHẦN ĐỊA CHỈ 5 BIT. DẠNG GỢI NHỚ CỦA LỆNH MÁY NHƯ SAU: TÊN LỆNH XXXXX, TRONG ĐÓ XXXXX LÀ SỐ NHỊ PHÂN 5 BIT. LỆNH LOAD XXXXX THỰC HIỆN NẠP NỘI DUNG Ô NHỚ ĐỊA CHỈ XXXXX VÀO THANH TÍCH LŨY ACC. GIẢ SỬ ACC ĐANG CHỨA GIÁ TRỊ 01101, Ô NHỚ 10110 CHỨA GIÁ TRỊ 10101. VẬY KHI THỰC HIỆN LỆNH LOAD 10110, ACC SẼ CÓ GIÁ TRỊ LÀ BAO NHIÊU?

Bài giải chi tiết:

Lệnh LOAD XXXXX là một lệnh máy đơn giản có chức năng đọc dữ liệu từ một vị trí bộ nhớ cụ thể (được chỉ định bởi XXXXX) và ghi nó vào thanh ghi tích lũy (Accumulator – ACC). Thanh ghi ACC là một thanh ghi đa năng trong CPU, thường được sử dụng để lưu trữ các toán hạng và kết quả của các phép toán số học và logic.

- Cấu trúc lệnh: Lệnh có dạng “Tên lệnh XXXXX”, trong đó XXXXX là địa chỉ bộ nhớ dưới dạng số nhị phân 5 bit. Điều này có nghĩa là chúng ta có thể địa chỉ hóa $2^5 = 32$ vị trí bộ nhớ khác nhau.

- Lệnh LOAD XXXXX: Hoạt động là

ACC <- M[XXXXX], tức là nội dung của ô nhớ tại địa chỉ XXXXX sẽ được chuyển vào thanh ghi ACC.

Trong trường hợp này:

- ACC ban đầu chứa giá trị:

01101 - Ô nhớ có địa chỉ

10110chứa giá trị:10101 - Lệnh cần thực hiện là

LOAD 10110.

Theo định nghĩa của lệnh LOAD, nội dung của ô nhớ 10110 sẽ được nạp vào ACC.

Vậy, sau khi thực hiện lệnh LOAD 10110, thanh ghi ACC sẽ có giá trị là 10101.

Bài 2: XÉT MỘT MÁY TÍNH VỚI TẬP LỆNH MÁY KHUÔN DẠNG 8-BIT, VỚI PHẦN ĐỊA CHỈ CHỈ CÓ MỘT ĐỊA CHỈ 5 BIT. DẠNG GỢI NHỚ CỦA LỆNH MÁY NHƯ SAU: TÊN LỆNH XXXXX, TRONG ĐÓ XXXXX LÀ SỐ NHỊ PHÂN 5 BIT. LỆNH STORE XXXXX THỰC HIỆN CẤT NỘI DUNG THANH TÍCH LŨY ACC RA Ô NHỚ ĐỊA CHỈ XXXXX. GIẢ SỬ ACC CHỨA GIÁ TRỊ 11001, KHI LỆNH STORE 11010 ĐƯỢC THỰC HIỆN THÌ Ô NHỚ ĐÍCH SẼ CÓ GIÁ TRỊ LÀ BAO NHIÊU?

Bài giải chi tiết:

Lệnh STORE XXXXX là lệnh ngược lại của LOAD, có chức năng ghi dữ liệu từ thanh ghi ACC vào một vị trí bộ nhớ cụ thể.

- Lệnh STORE XXXXX: Hoạt động là

M[XXXXX] <- ACC, tức là nội dung của thanh ghi ACC sẽ được chuyển vào ô nhớ tại địa chỉ XXXXX.

Trong trường hợp này:

- ACC đang chứa giá trị:

11001 - Lệnh cần thực hiện là

STORE 11010.

Theo định nghĩa của lệnh STORE, nội dung của ACC (11001) sẽ được cất vào ô nhớ tại địa chỉ 11010.

Vậy, sau khi thực hiện lệnh STORE 11010, ô nhớ đích 11010 sẽ có giá trị là 11001.

Ví dụ bài tập kiến trúc máy tính

Bài 3: XÉT MỘT MÁY TÍNH VỚI TẬP LỆNH MÁY KHUÔN DẠNG 8-BIT, VỚI PHẦN ĐỊA CHỈ CHỈ CÓ MỘT ĐỊA CHỈ 5 BIT. DẠNG GỢI NHỚ CỦA LỆNH MÁY NHƯ SAU: TÊN LỆNH XXXXX, TRONG ĐÓ XXXXX LÀ SỐ NHỊ PHÂN 5 BIT. LỆNH CỘNG ADD XXXXX THỰC HIỆN CỘNG NỘI DUNG THANH GHI ACC VỚI NỘI DUNG Ô NHỚ ĐỊA CHỈ XXXXX, KẾT QUẢ CHỨA VÀO ACC. LỆNH LOAD XXXXX THỰC HIỆN NHẬP NỘI DUNG Ô NHỚ ĐỊA CHỈ XXXXX VÀO ACC. HÃY KHẢO SÁT QUÁ TRÌNH ĐƠN VỊ XỬ LÝ TRUNG TÂM THỰC HIỆN TUẦN TỰ HAI LỆNH SAU: LOAD 01110, ADD 10001. GIẢ ĐỊNH Ô NHỚ 01110 CHỨA GIÁ TRỊ 10010, Ô NHỚ 10001 CHỨA GIÁ TRỊ 01001. VẬY SAU KHI THỰC HIỆN XONG LỆNH ADD, THANH CHỨA ACC SẼ CÓ GIÁ TRỊ LÀ BAO NHIÊU?

Bài giải chi tiết:

Trong bài tập này, chúng ta cần thực hiện một chuỗi hai lệnh: LOAD và ADD. Đây là một ví dụ điển hình về cách CPU xử lý các lệnh theo tuần tự, cập nhật trạng thái của thanh ghi ACC sau mỗi thao tác.

- Lệnh LOAD XXXXX:

ACC <- M[XXXXX](nạp nội dung từ ô nhớ XXXXX vào ACC). - Lệnh ADD XXXXX:

ACC <- ACC + M[XXXXX](cộng nội dung ACC với nội dung từ ô nhớ XXXXX, kết quả lưu vào ACC).

Các giá trị ban đầu và ô nhớ:

- Ô nhớ

01110chứa giá trị:10010 - Ô nhớ

10001chứa giá trị:01001

Quá trình thực hiện lệnh:

- Thực hiện lệnh LOAD 01110:

- Nội dung của ô nhớ

01110(10010) được nạp vào ACC. - Sau lệnh này, ACC sẽ có giá trị:

10010.

- Nội dung của ô nhớ

- Thực hiện lệnh ADD 10001:

- Nội dung hiện tại của ACC (

10010) sẽ được cộng với nội dung của ô nhớ10001(01001). - Thực hiện phép cộng nhị phân:

10010 (ACC)

-

01001 (M[10001])

11011 (Kết quả mới trong ACC)

- Sau lệnh này, ACC sẽ có giá trị:

11011.

- Nội dung hiện tại của ACC (

Vậy, sau khi thực hiện xong lệnh ADD, thanh ghi ACC sẽ có giá trị là 11011. Đây là một dạng bài tập kiến trúc máy tính cơ bản giúp bạn hiểu rõ luồng dữ liệu.

Giải bài tập kiến trúc máy tính

Bài tập về Thanh ghi và Hoạt động dữ liệu

Tiếp theo, chúng ta sẽ khám phá các bài tập liên quan đến hoạt động của các thanh ghi X và Y, cũng như các lệnh như ADD và MOVE trong ngữ cảnh của kiến trúc máy tính với các giá trị dạng mã Hexa. Việc chuyển đổi giữa các hệ cơ số và hiểu rõ cơ chế truyền dữ liệu là trọng tâm của phần này.

Bài 1: CHO MỘT ĐƠN VỊ XỬ LÝ TRUNG TÂM CÓ KHẢ NĂNG XỬ LÝ TẬP LỆNH MÁY DẠNG OP A, B. KÝ HIỆU X, Y LÀ CÁC THANH GHI CỦA ĐƠN VỊ XỬ LÝ TRUNG TÂM. LỆNH MÁY ADD A, B THỰC HIỆN CỘNG GIÁ TRỊ TOÁN HẠNG TỪ NGUỒN B VỚI NGUỒN A, KẾT QUẢ CHỨA VÀO A. KÝ HIỆU XXXXH LÀ MỘT CON SỐ DẠNG MÃ HEXA. CHO CÁC GIÁ TRỊ BAN ĐẦU X= 1B23H, Y = 02C4H. HÃY XÁC ĐỊNH GIÁ TRỊ CỦA CÁC THANH GHI X VÀ Y SAU KHI ĐƠN VỊ XỬ LÝ TRUNG TÂM THỰC HIỆN LỆNH ADD Y,X.

Bài giải chi tiết:

Bài tập này yêu cầu thực hiện phép cộng trên các giá trị Hexadecimal và hiểu cách lệnh ADD hoạt động với các thanh ghi.

- Lệnh ADD A, B: Hoạt động là

A <- A + B. Toán hạng từ B được cộng vào A, kết quả lưu vào A. - Giá trị ban đầu:

- X =

1B23H - Y =

02C4H

- X =

- Lệnh cần thực hiện:

ADD Y, X. Điều này có nghĩa làY <- Y + X. Giá trị của X sẽ được cộng vào Y, và kết quả sẽ được lưu vào Y. Giá trị của X sẽ không thay đổi.

Bước 1: Chuyển đổi các giá trị Hexa sang Nhị phân để dễ dàng thực hiện phép cộng (hoặc có thể cộng trực tiếp trên hệ Hexa).

- X =

1B23H=0001 1011 0010 0011(16 bit) - Y =

02C4H=0000 0010 1100 0100(16 bit)

Bước 2: Thực hiện phép cộng nhị phân Y + X.

0000 0010 1100 0100 (Y)

+ 0001 1011 0010 0011 (X)

-----------------------

0001 1101 1110 0111Bước 3: Chuyển kết quả trở lại dạng Hexadecimal.

0001 1101 1110 0111 = 1DE7H

Bước 4: Xác định giá trị cuối cùng của các thanh ghi.

- Sau khi thực hiện lệnh

ADD Y, X, thanh ghi Y sẽ chứa kết quả của phép cộng. - Thanh ghi X không bị ảnh hưởng bởi lệnh này.

Vậy, sau khi thực hiện lệnh ADD Y, X:

- X =

1B23H - Y =

1DE7H

Đây là một ví dụ điển hình về việc thực hành các bài tập kiến trúc máy tính liên quan đến thao tác thanh ghi.

Bài tập thanh ghi kiến trúc máy tính

Bài 2: CHO MỘT ĐƠN VỊ XỬ LÝ TRUNG TÂM CÓ KHẢ NĂNG XỬ LÝ TẬP LỆNH MÁY DẠNG OP A, B. LỆNH MÁY MOVE A, B THỰC HIỆN CHUYỂN GIÁ TRỊ TOÁN HẠNG TỪ NGUỒN B ĐẾN ĐÍCH A. KÝ HIỆU X, Y LÀ CÁC THANH GHI CỦA ĐƠN VỊ XỬ LÝ TRUNG TÂM. KÝ HIỆU XXXXH LÀ MỘT CON SỐ DẠNG MÃ HEXA. CHO X= (0A37H, Y = 012CH). HÃY XÁC ĐỊNH GIÁ TRỊ CỦA CÁC THANH GHI X VÀ Y SAU KHI ĐƠN VỊ XỬ LÝ TRUNG TÂM THỰC HIỆN LỆNH MOVE Y,X.

Bài giải chi tiết:

Lệnh MOVE là một trong những lệnh cơ bản nhất, dùng để sao chép dữ liệu từ một nguồn sang một đích.

- Lệnh MOVE A, B: Hoạt động là

A <- B. Nội dung của toán hạng nguồn B được sao chép vào toán hạng đích A. Giá trị của nguồn B không thay đổi sau thao tác này. - Giá trị ban đầu:

- X =

0A37H - Y =

012CH

- X =

- Lệnh cần thực hiện:

MOVE Y, X. Điều này có nghĩa là nội dung của X sẽ được sao chép vào Y (Y <- X).

Thực hiện lệnh:

Giá trị của X (0A37H) sẽ được sao chép vào thanh ghi Y. Giá trị của X vẫn giữ nguyên.

Vậy, sau khi thực hiện lệnh MOVE Y, X:

- X =

0A37H - Y =

0A37H

Lưu ý rằng trong nhiều kiến trúc CPU thực tế, lệnh MOVE thường chỉ sao chép giá trị, không làm “xóa” giá trị gốc như một số người nhầm tưởng. Đây là một điểm quan trọng khi giải các bài tập kiến trúc máy tính liên quan đến việc truyền dữ liệu.

Thực hành bài tập kiến trúc máy tính

Bài 3: CHO MỘT ĐƠN VỊ XỬ LÝ TRUNG TÂM CÓ KHẢ NĂNG XỬ LÝ TẬP LỆNH MÁY DẠNG OP A, B. LỆNH MÁY MOVE A, B THỰC HIỆN CHUYỂN GIÁ TRỊ TOÁN HẠNG TỪ NGUỒN B ĐẾN ĐÍCH A. KÝ HIỆU X VÀ Y LÀ CÁC THANH GHI CỦA ĐƠN VỊ XỬ LÝ TRUNG TÂM. KÝ HIỆU XXXXH LÀ MỘT CON SỐ DẠNG MÃ HEXA. KÝ HIỆU [R] LÀ NỘI DUNG Ô NHỚ MÀ ĐỊA CHỈ CỦA NÓ ĐƯỢC XÁC ĐỊNH BỞI THANH GHI R. GIẢ ĐỊNH X = 1853H VÀ Y= 5140H, Ô NHỚ ĐỊA CHỈ 5140H ĐANG CHỨA GIÁ TRỊ 2040H. SAU KHI ĐƠN VỊ XỬ LÝ TRUNG TÂM THỰC HIỆN LỆNH MOVE X, [Y] THÌ THANH GHI X CÓ GIÁ TRỊ LÀ BAO NHIÊU?

Bài giải chi tiết:

Bài tập này giới thiệu khái niệm địa chỉ gián tiếp thông qua thanh ghi, một phương thức địa chỉ hóa phổ biến trong kiến trúc máy tính.

- Lệnh MOVE A, B:

A <- B. - Ký hiệu [R]: Biểu thị nội dung của ô nhớ mà địa chỉ của nó được lưu trong thanh ghi R.

- Giá trị ban đầu:

- Thanh ghi X =

1853H - Thanh ghi Y =

5140H - Ô nhớ tại địa chỉ

5140Hchứa giá trị:2040H

- Thanh ghi X =

- Lệnh cần thực hiện:

MOVE X, [Y]. Điều này có nghĩa là nội dung của ô nhớ mà địa chỉ của nó nằm trong thanh ghi Y sẽ được sao chép vào thanh ghi X (X <- M[Y]).

Thực hiện lệnh:

- Xác định địa chỉ nguồn: Thanh ghi Y chứa

5140H, vì vậy[Y]tham chiếu đến nội dung của ô nhớ tại địa chỉ5140H. - Nội dung của ô nhớ

5140Hlà2040H. - Giá trị này (

2040H) sẽ được sao chép vào thanh ghi X.

Vậy, sau khi thực hiện lệnh MOVE X, [Y], thanh ghi X sẽ có giá trị là 2040H. Giá trị của Y và ô nhớ 5140H không thay đổi.

Bài 4: KÝ HIỆU XXXXH LÀ MỘT SỐ DẠNG MÃ HEXA. CHO MỘT TẬP LỆNH CÓ KHUÔN DẠNG 16 BIT, 4 BIT ĐẦU TIÊN LÀ MÃ THAO TÁC VÀ LỆNH CHỈ CÓ MỘT THÀNH PHẦN ĐỊA CHỈ. CHO BỘ NHỚ CÓ Ô NHỚ RỘNG 16 BIT. LỆNH MÁY STORE XXXH THỰC HIỆN SAO NỘI DUNG ACC RA Ô NHỚ CÓ ĐỊA CHỈ XXXH XÁC ĐỊNH TRÊN LỆNH. CHO ACC=0637H, CON TRỎ LỆNH PC= 354H , Ô NHỚ 354H CHỨA LỆNH STORE 485H, Ô NHỚ 485H CHỨA GIÁ TRỊ 2323H. SAU TIỂU CHU KỲ THỰC HIỆN LỆNH STORE 485H, THANH GHI MAR CÓ GIÁ TRỊ LÀ BAO NHIÊU?

Bài giải chi tiết:

Bài tập này đòi hỏi sự hiểu biết về chu kỳ thực hiện lệnh (Fetch-Decode-Execute) và vai trò của các thanh ghi như Program Counter (PC) và Memory Address Register (MAR).

- Lệnh STORE XXXH:

M[XXXH] <- ACC. - Các giá trị ban đầu:

- ACC =

0637H - PC =

354H - Ô nhớ

354Hchứa lệnhSTORE 485H - Ô nhớ

485Hchứa giá trị2323H

- ACC =

Phân tích chu kỳ lệnh và vai trò của MAR:

Trong một chu kỳ thực hiện lệnh cơ bản, có hai giai đoạn chính:

- Giai đoạn Fetch (tìm nạp lệnh):

- CPU nạp nội dung của PC vào MAR (

MAR <- PC). MAR sẽ chứa địa chỉ của lệnh cần được tìm nạp. - Sau đó, CPU sẽ đọc lệnh từ địa chỉ trong MAR vào Memory Buffer Register (MBR) hoặc Instruction Register (IR).

- PC được tăng lên để trỏ đến lệnh tiếp theo.

- CPU nạp nội dung của PC vào MAR (

- Giai đoạn Execute (thực thi lệnh):

- Lệnh trong IR/MBR được giải mã.

- Các thao tác cần thiết được thực hiện. Nếu lệnh yêu cầu truy cập bộ nhớ (như STORE), địa chỉ dữ liệu sẽ được đưa vào MAR.

Thực hiện các bước:

- Trước chu kỳ thực hiện lệnh STORE 485H:

- PC đang trỏ đến lệnh

STORE 485Htại địa chỉ354H. - Vậy, ở đầu giai đoạn Fetch của lệnh này, giá trị của PC (

354H) sẽ được chuyển vào MAR. - Lúc này, MAR =

354H.

- PC đang trỏ đến lệnh

- Giai đoạn Fetch hoàn tất: Lệnh

STORE 485Hđược nạp vào CPU, và PC tăng lên (ví dụ:PC = 354H + kích thước_lệnh). - Giai đoạn Execute của lệnh STORE 485H:

- CPU giải mã lệnh

STORE 485H. Nó hiểu rằng cần ghi nội dung của ACC vào ô nhớ có địa chỉ485H. - Để thực hiện thao tác ghi này, CPU cần đưa địa chỉ đích (

485H) vào MAR (MAR <- 485H). - Sau đó, nội dung của ACC (

0637H) sẽ được ghi vào ô nhớ tại địa chỉ485H.

- CPU giải mã lệnh

Vậy, sau tiểu chu kỳ thực hiện lệnh STORE 485H (tức là sau khi lệnh đã được giải mã và địa chỉ đích đã sẵn sàng cho thao tác ghi), thanh ghi MAR sẽ có giá trị là 485H. Đáp án 0637H trong bài gốc có vẻ là nhầm lẫn với giá trị của ACC sau lệnh. MAR sẽ chứa địa chỉ của dữ liệu được truy cập trong giai đoạn thực thi.

Các câu hỏi trắc nghiệm Kiến trúc Máy tính có lời giải chi tiết

Phần này sẽ trình bày các câu hỏi trắc nghiệm và lời giải thích sâu sắc hơn, giúp bạn không chỉ tìm được đáp án mà còn hiểu rõ bản chất của vấn đề.

Kiến trúc cơ bản của máy tính điện tử (Chương 1)

Câu 1: TRONG ĐƠN VỊ XỬ LÝ TRUNG TÂM, DỰA TRÊN THÔNG TIN NÀO ĐƠN VỊ ĐIỀU KHIỂN CU SINH RA CÁC TÍN HIỆU ĐIỀU KHIỂN?

Trả lời và giải thích chi tiết:

Đơn vị điều khiển (Control Unit – CU) là bộ não của CPU, chịu trách nhiệm điều phối tất cả các hoạt động bên trong CPU và giữa CPU với các thành phần khác của hệ thống. Để sinh ra các tín hiệu điều khiển chính xác, CU cần thông tin về lệnh mà nó đang xử lý.

Thông tin mà CU sử dụng chính là mã thao tác (opcode) của mã lệnh máy. Mỗi lệnh máy có một mã thao tác riêng biệt, cho CPU biết loại hoạt động cần thực hiện (ví dụ: ADD, LOAD, STORE). Khi một lệnh được nạp vào CPU (cụ thể là vào thanh ghi lệnh – Instruction Register), CU sẽ giải mã mã thao tác này. Dựa trên mã thao tác, CU sẽ tạo ra một chuỗi các tín hiệu điều khiển vi mô (micro-operations) để kích hoạt các thành phần phần cứng phù hợp (ví dụ: bộ số học/logic ALU, các thanh ghi, bus) để thực hiện lệnh đó. Các tín hiệu này bao gồm các lệnh điều khiển như đọc/ghi thanh ghi, cho phép/không cho phép bus, chọn chức năng của ALU, v.v.

Vì vậy, đáp án chính xác là: Các thông tin chứa trong mã thao tác của mã lệnh máy.

Câu hỏi trắc nghiệm kiến trúc máy tính

Câu 2: CHỨC NĂNG CỦA CON TRỎ LỆNH PC (PROGRAM COUNTER) TRONG ĐƠN VỊ XỬ LÝ TRUNG TÂM LÀ GÌ?

Trả lời và giải thích chi tiết:

Con trỏ lệnh (Program Counter – PC), còn được gọi là Thanh ghi con trỏ lệnh (Instruction Pointer – IP) trong kiến trúc Intel x86, đóng vai trò cực kỳ quan trọng trong việc điều khiển luồng thực thi của chương trình.

- Chức năng chính: PC luôn chứa địa chỉ bộ nhớ của lệnh tiếp theo mà CPU sẽ tìm nạp và thực thi. Nó hoạt động như một “đánh dấu” cho vị trí hiện tại trong chương trình.

- Hoạt động cụ thể:

- Khởi tạo: Khi một chương trình bắt đầu, PC được nạp địa chỉ của lệnh đầu tiên của chương trình.

- Trong chu kỳ Fetch: Ở đầu mỗi chu kỳ lệnh, nội dung của PC được sao chép vào Thanh ghi địa chỉ bộ nhớ (MAR) để CPU có thể truy cập lệnh từ bộ nhớ.

- Tự động tăng: Sau khi lệnh hiện tại được tìm nạp (hoặc đôi khi ngay sau khi bắt đầu giai đoạn fetch), PC tự động tăng lên một lượng bằng kích thước của lệnh vừa nạp, để trỏ đến lệnh kế tiếp trong trình tự chương trình. Điều này đảm bảo CPU thực thi các lệnh theo đúng thứ tự.

- Thay đổi luồng: Trong trường hợp các lệnh nhảy (JUMP), gọi chương trình con (CALL), hoặc các lệnh điều kiện (IF), giá trị của PC có thể bị thay đổi một cách có điều kiện hoặc vô điều kiện, làm thay đổi luồng thực thi bình thường của chương trình.

- Kích thước: Kích thước của PC phụ thuộc vào kiến trúc CPU (ví dụ: 8, 16, 32, 64 bit), quyết định phạm vi địa chỉ bộ nhớ mà CPU có thể truy cập.

Tóm lại, PC đảm bảo CPU biết được lệnh nào cần thực thi tiếp theo, duy trì trật tự và khả năng thay đổi luồng điều khiển của chương trình.

Câu 3: QUÁ TRÌNH THỰC HIỆN MỘT LỆNH MÁY ĐƯỢC ĐIỀU KHIỂN BỞI ĐƠN VỊ CHỨC NĂNG NÀO TRONG ĐƠN VỊ XỬ LÝ TRUNG TÂM?

Trả lời và giải thích chi tiết:

Quá trình thực hiện một lệnh máy là một chuỗi các thao tác vi mô phức tạp, từ việc tìm nạp lệnh, giải mã đến thực thi và lưu kết quả. Đơn vị chức năng chịu trách nhiệm điều phối toàn bộ quá trình này trong CPU là Khối điều khiển (Control Unit – CU).

- Vai trò của CU:

- Giải mã lệnh: CU nhận lệnh từ Thanh ghi lệnh (Instruction Register) và giải mã mã thao tác (opcode) để xác định loại lệnh và các toán hạng liên quan.

- Sinh tín hiệu điều khiển: Dựa trên kết quả giải mã, CU tạo ra các chuỗi tín hiệu điều khiển đúng thời điểm, gửi đến các thành phần khác của CPU (ví dụ: Bộ số học/logic ALU, các thanh ghi) và các thành phần ngoại vi (bộ nhớ, thiết bị I/O).

- Điều phối hoạt động: Các tín hiệu này điều khiển hoạt động của bus dữ liệu, bus địa chỉ, bus điều khiển, cho phép/không cho phép các cổng, chọn phép toán của ALU, và quản lý luồng dữ liệu giữa các thanh ghi.

- Đảm bảo trình tự: CU đảm bảo rằng các vi thao tác (micro-operations) cần thiết để thực hiện một lệnh diễn ra theo đúng trình tự và thời gian quy định.

Ví dụ, khi một lệnh ADD được thực hiện, CU sẽ sinh ra các tín hiệu để: đọc toán hạng từ bộ nhớ vào một thanh ghi, đọc toán hạng thứ hai từ một thanh ghi khác, kích hoạt ALU thực hiện phép cộng, và ghi kết quả trở lại thanh ghi hoặc bộ nhớ. Tất cả các bước này được điều khiển chặt chẽ bởi CU.

Trắc nghiệm kiến trúc máy tính có đáp án

Ôn tập chương 2: Đơn vị xử lý trung tâm

Câu 1: TRONG ĐƠN VỊ ĐIỀU KHIỂN VI LẬP TRÌNH, CÁC TÍN HIỆU ĐIỀU KHIỂN CẦN CÓ ĐƯỢC BIỂU DIỄN VÀ ĐƯỢC HOẠT HÓA BỞI CÁI GÌ?

Trả lời và giải thích chi tiết:

Trong đơn vị điều khiển vi lập trình (Microprogrammed Control Unit), thay vì sử dụng mạch logic cố định (Hardwired Control Unit), các tín hiệu điều khiển được tạo ra bằng cách thực thi một chuỗi các “vi lệnh” (microinstructions) lưu trữ trong bộ nhớ điều khiển (Control Memory – CM).

- Biểu diễn tín hiệu điều khiển: Các tín hiệu điều khiển cần thiết cho mỗi vi thao tác được biểu diễn dưới dạng các bit trong một vi lệnh. Một vi lệnh là một từ dữ liệu có định dạng đặc biệt, với các trường bit khác nhau. Mỗi trường bit này điều khiển một hoặc nhiều chức năng cụ thể của CPU (ví dụ: cho phép ghi vào thanh ghi X, kích hoạt cổng bus Y, chọn phép toán của ALU).

- Hoạt hóa tín hiệu điều khiển:

- Trường điều khiển (Control Field): Là phần của vi lệnh chứa các bit điều khiển trực tiếp các hoạt động của CPU. Khi vi lệnh được đọc từ bộ nhớ điều khiển, các bit trong trường này sẽ kích hoạt các cổng, đường dẫn dữ liệu, và các đơn vị chức năng khác.

- Trường địa chỉ (Address Field) hoặc Logic rẽ nhánh (Branch Logic): Đây là phần quan trọng giúp xác định vi lệnh tiếp theo sẽ được thực thi. Sau khi một vi lệnh được thực thi, CU cần biết vi lệnh nào sẽ được nạp tiếp theo để tiếp tục chuỗi các vi thao tác cho lệnh máy hiện tại, hoặc để chuyển sang vi thủ tục của lệnh máy khác. Trường địa chỉ có thể chỉ ra địa chỉ của vi lệnh tiếp theo, hoặc cung cấp thông tin để một bộ tạo địa chỉ vi lệnh (Microinstruction Address Generator) quyết định địa chỉ kế tiếp dựa trên các cờ trạng thái.

Vì vậy, các tín hiệu điều khiển được biểu diễn bởi các tập vi lệnh dưới dạng bit và được hoạt hóa bởi trường điều khiển và trường địa chỉ/logic rẽ nhánh trong vi lệnh đó.

Câu 2: TRONG ĐƠN VỊ ĐIỀU KHIỂN VI LẬP TRÌNH, NỘI DUNG MỖI MỘT VI THỦ TỤC PHẢN ÁNH CÁI GÌ?

Trả lời và giải thích chi tiết:

Một vi thủ tục (microprogram) trong đơn vị điều khiển vi lập trình là một chuỗi các vi lệnh được lưu trữ trong bộ nhớ điều khiển. Mỗi vi thủ tục tương ứng với việc thực hiện một lệnh máy cụ thể (ví dụ: một vi thủ tục cho lệnh ADD, một cho lệnh LOAD).

Nội dung của mỗi vi thủ tục phản ánh chuỗi các vi thao tác (micro-operations) cần thiết để thực hiện một lệnh máy theo đúng trình tự và thời gian. Nó định nghĩa chính xác những gì CPU phải làm ở cấp độ phần cứng để hoàn thành một lệnh.

Cụ thể, vi thủ tục bao gồm:

- Trật tự các vi thao tác: Các vi lệnh trong vi thủ tục được sắp xếp theo một trình tự logic, đảm bảo rằng các bước nhỏ nhất (như đọc từ thanh ghi, ghi vào bus, thực hiện phép cộng) diễn ra đúng thứ tự.

- Thời điểm kích hoạt tín hiệu điều khiển: Mỗi vi lệnh trong vi thủ tục được thực thi tại một chu kỳ xung nhịp cụ thể, và các bit điều khiển trong vi lệnh đó sẽ kích hoạt các tín hiệu điều khiển tương ứng vào đúng thời điểm. Điều này đảm bảo đồng bộ hóa chính xác giữa các hoạt động phần cứng.

- Logic điều khiển luồng: Vi thủ tục cũng chứa logic để rẽ nhánh, lặp lại hoặc kết thúc dựa trên trạng thái của CPU hoặc các cờ điều kiện.

Tóm lại, nội dung một vi thủ tục là bộ hướng dẫn chi tiết, từng bước ở cấp độ phần cứng (vi thao tác) để thực thi một lệnh máy nhất định, đảm bảo các tín hiệu điều khiển được tạo ra đúng lúc và theo đúng trình tự.

Bus và vấn đề truyền thông tin trong máy tính

Câu 1: DỰA VÀO ĐÂU MÀ ĐƠN VỊ XỬ LÝ TRUNG TÂM CÓ THỂ KẾT NỐI VÀ TRAO ĐỔI THÔNG TIN VỚI NHIỀU ĐỐI TƯỢNG (THIẾT BỊ) KHÁC NHAU TRÊN CÙNG MỘT ĐƯỜNG BUS CHUNG MÀ KHÔNG BỊ XUNG ĐỘT?

Trả lời và giải thích chi tiết:

Để CPU có thể giao tiếp với nhiều thiết bị (bộ nhớ, thiết bị I/O) trên cùng một bus chung mà không xảy ra xung đột, hệ thống máy tính sử dụng các cơ chế quản lý và địa chỉ hóa.

- Địa chỉ hóa và giải mã địa chỉ:

- Địa chỉ duy nhất: Mỗi thiết bị hoặc ô nhớ trong hệ thống được gán một địa chỉ duy nhất. Khi CPU muốn giao tiếp với một thiết bị cụ thể, nó sẽ đặt địa chỉ của thiết bị đó lên bus địa chỉ.

- Bộ giải mã địa chỉ (Address Decoder): Mỗi thiết bị ngoại vi hoặc khối bộ nhớ đều có một bộ giải mã địa chỉ riêng. Bộ giải mã này liên tục giám sát bus địa chỉ. Khi địa chỉ trên bus khớp với địa chỉ được gán cho thiết bị đó, bộ giải mã sẽ kích hoạt thiết bị, cho phép nó phản hồi. Các thiết bị khác có bộ giải mã không khớp địa chỉ sẽ không được kích hoạt và giữ trạng thái “ngủ”, không gây xung đột trên bus.

- Đường điều khiển (Control Lines): Bus điều khiển chứa các tín hiệu để quản lý việc truy cập bus và loại bỏ xung đột:

- Tín hiệu đọc/ghi (Read/Write): CPU gửi tín hiệu này để cho thiết bị biết liệu nó muốn đọc hay ghi dữ liệu.

- Tín hiệu chọn chip (Chip Select – CS): Tín hiệu này, thường được tạo ra từ bộ giải mã địa chỉ, là cần thiết để kích hoạt một chip cụ thể. Chỉ chip nào được chọn mới có thể hoạt động.

- Tín hiệu chờ (Wait State): Cho phép các thiết bị chậm hơn báo cho CPU biết cần thêm thời gian để hoàn tất giao dịch, ngăn CPU đọc hoặc ghi dữ liệu quá nhanh.

- Cổng vào/ra 3 trạng thái (Three-State Buffers/Gates): Các thiết bị kết nối với bus dữ liệu thông qua các cổng 3 trạng thái. Ở trạng thái bình thường (không được chọn), các cổng này ở trạng thái trở kháng cao (high-impedance), giống như bị ngắt kết nối hoàn toàn khỏi bus, không truyền hay nhận tín hiệu gì. Chỉ khi thiết bị được bộ giải mã địa chỉ chọn và CPU gửi tín hiệu điều khiển thích hợp, các cổng này mới được kích hoạt để truyền hoặc nhận dữ liệu.

Nhờ những cơ chế này, tại một thời điểm, chỉ có duy nhất một thiết bị được phép giao tiếp với CPU trên bus dữ liệu, tránh được xung đột thông tin.

Câu 2: TẠI SAO KỸ THUẬT ĐỊNH THỜI ĐỒNG BỘ ĐƯỢC CHỌN ĐỂ THỰC HIỆN TRAO ĐỔI THÔNG TIN GIỮA ĐƠN VỊ XỬ LÝ TRUNG TÂM VỚI CÁC ĐỐI TƯỢNG BÊN TRONG HỆ THỐNG MÁY TÍNH?

Trả lời và giải thích chi tiết:

Kỹ thuật định thời đồng bộ (Synchronous Timing) được ưu tiên sử dụng để trao đổi thông tin giữa CPU và các đối tượng bên trong hệ thống (như bộ nhớ chính, bộ nhớ cache) vì những lý do sau:

- Tốc độ cao và hiệu quả: Trong kỹ thuật đồng bộ, tất cả các hoạt động trên bus được điều khiển bởi một tín hiệu đồng hồ (clock signal) chung. Các sự kiện (như đặt địa chỉ, gửi dữ liệu) xảy ra tại các cạnh (lên hoặc xuống) của xung đồng hồ. Điều này cho phép các thành phần hoạt động ở tốc độ tối đa của xung đồng hồ, tối ưu hóa băng thông của bus.

- Đơn giản trong thiết kế và kiểm soát: Với một đồng hồ chung, việc thiết kế các mạch điều khiển trở nên đơn giản hơn nhiều. CPU chỉ cần biết thời điểm gửi tín hiệu và thời điểm nhận phản hồi, dựa trên chu kỳ đồng hồ. Các thiết bị cũng được thiết kế để hoạt động theo cùng một nhịp độ.

- Tính nhất quán: Các thành phần bên trong hệ thống máy tính (CPU, RAM, Cache) thường được thiết kế để có tốc độ hoạt động tương đương hoặc rất gần nhau. Do đó, việc sử dụng định thời đồng bộ đảm bảo tất cả chúng hoạt động cùng một nhịp, giảm thiểu độ trễ và tăng tính ổn định của hệ thống.

- Không cần tín hiệu bắt tay (handshake): Không giống như định thời không đồng bộ, định thời đồng bộ không yêu cầu các tín hiệu “bắt tay” phức tạp (ví dụ: “data ready”, “ack”). Điều này giúp giảm số lượng đường điều khiển và độ phức tạp của giao thức giao tiếp, góp phần tăng tốc độ.

Tuy nhiên, định thời đồng bộ chỉ hiệu quả khi tất cả các thiết bị đều có thể phản hồi trong cùng một khoảng thời gian đồng hồ. Nếu có thiết bị quá chậm, nó sẽ không thể theo kịp, dẫn đến lỗi hoặc cần cơ chế chờ (wait state) bổ sung. Vì các thành phần nội bộ được tối ưu hóa cho tốc độ, nên định thời đồng bộ là lựa chọn tối ưu.

Câu 3: TẠI SAO KỸ THUẬT ĐỊNH THỜI KHÔNG ĐỒNG BỘ ĐƯỢC CHỌN ĐỂ THỰC HIỆN TRAO ĐỔI THÔNG TIN GIỮA ĐƠN VỊ XỬ LÝ TRUNG TÂM VỚI CÁC ĐỐI TƯỢNG BÊN NGOÀI HỆ THỐNG MÁY TÍNH?

Trả lời và giải thích chi tiết:

Kỹ thuật định thời không đồng bộ (Asynchronous Timing) được sử dụng để trao đổi thông tin giữa CPU và các thiết bị ngoại vi (bên ngoài hệ thống) vì sự khác biệt lớn về tốc độ hoạt động giữa CPU và các thiết bị này.

- Khác biệt tốc độ lớn: Các thiết bị ngoại vi (như máy in, ổ cứng, bàn phím, chuột, thiết bị mạng) hoạt động chậm hơn CPU rất nhiều. Định thời đồng bộ không phù hợp vì CPU sẽ phải chờ rất lâu cho thiết bị chậm, hoặc thiết bị chậm sẽ không kịp phản hồi trước khi chu kỳ đồng hồ kết thúc.

- Linh hoạt và khả năng tương thích: Định thời không đồng bộ cho phép các thiết bị có tốc độ khác nhau giao tiếp với CPU. CPU không cần biết chính xác tốc độ của thiết bị; thay vào đó, chúng sử dụng các tín hiệu “bắt tay” (handshake signals) để thông báo khi dữ liệu sẵn sàng hoặc khi đã nhận được dữ liệu. Điều này mang lại sự linh hoạt cao và khả năng tương thích với nhiều loại thiết bị từ các nhà sản xuất khác nhau.

- Cơ chế bắt tay:

- Khi CPU muốn ghi dữ liệu, nó sẽ đặt dữ liệu và địa chỉ lên bus, sau đó gửi tín hiệu “write request”. Thiết bị sẽ xử lý dữ liệu và gửi tín hiệu “write acknowledge” khi hoàn tất.

- Khi CPU muốn đọc, nó gửi “read request”. Thiết bị sẽ đặt dữ liệu lên bus và gửi “data ready”. CPU sau đó sẽ đọc dữ liệu và gửi “read acknowledge”.

- Độ tin cậy: Mặc dù chậm hơn, phương pháp này đảm bảo độ tin cậy của việc truyền dữ liệu, vì không có dữ liệu nào được bỏ qua do chênh lệch tốc độ. Mọi giao dịch đều được xác nhận.

Tóm lại, định thời không đồng bộ là cần thiết để CPU có thể giao tiếp hiệu quả và đáng tin cậy với thế giới bên ngoài, nơi tốc độ và hành vi của các thiết bị có thể rất đa dạng và không thể đoán trước bằng một nhịp đồng hồ chung.

Tổ chức bộ nhớ (Chương 4)

Câu 1: VIỆC QUẢN LÝ BỘ NHỚ TÁC ĐỘNG ĐẾN THIẾT BỊ NHỚ VẬT LÝ NÀO TRONG HỆ THỐNG BỘ NHỚ VẬT LÝ NHIỀU MỨC?

Trả lời và giải thích chi tiết:

Việc quản lý bộ nhớ (Memory Management) là một chức năng quan trọng của hệ điều hành, nhằm điều phối việc sử dụng tài nguyên bộ nhớ một cách hiệu quả giữa các chương trình đang chạy. Trong hệ thống bộ nhớ vật lý nhiều mức (Memory Hierarchy), quản lý bộ nhớ tác động đến tất cả các thiết bị nhớ vật lý, nhưng chủ yếu tập trung vào bộ nhớ chính (Main Memory hay RAM) và bộ nhớ cache.

- Hệ thống bộ nhớ nhiều mức bao gồm:

- Thanh ghi CPU (CPU Registers): Nhanh nhất, dung lượng nhỏ nhất, nằm ngay trong CPU.

- Bộ nhớ Cache (Cache Memory): Nhanh thứ hai, dung lượng nhỏ hơn RAM, nằm giữa CPU và RAM.

- Bộ nhớ chính (Main Memory/RAM): Nhanh hơn bộ nhớ thứ cấp, dung lượng lớn hơn cache, là nơi các chương trình đang chạy và dữ liệu của chúng được lưu trữ tạm thời.

- Bộ nhớ thứ cấp (Secondary Storage/Hard Drive/SSD): Chậm nhất, dung lượng lớn nhất, dùng để lưu trữ lâu dài.

- Tác động chính của quản lý bộ nhớ:

- Bộ nhớ chính (RAM): Đây là trọng tâm chính của quản lý bộ nhớ. Hệ điều hành phải quyết định chương trình nào sẽ được nạp vào RAM, phân bổ các vùng nhớ cho chúng, bảo vệ các vùng nhớ của từng chương trình khỏi việc truy cập trái phép, và giải phóng bộ nhớ khi chương trình kết thúc. Các kỹ thuật như phân trang (paging), phân đoạn (segmentation), và bộ nhớ ảo (virtual memory) đều nhằm quản lý RAM hiệu quả.

- Bộ nhớ Cache: Quản lý cache thường được thực hiện bởi phần cứng (cache controller) một cách tự động, minh bạch với hệ điều hành. Tuy nhiên, hiệu quả của cache bị ảnh hưởng trực tiếp bởi cách các chương trình truy cập dữ liệu trong bộ nhớ chính. Một hệ điều hành quản lý bộ nhớ tốt có thể gián tiếp tối ưu hóa việc sử dụng cache bằng cách sắp xếp dữ liệu và mã lệnh hợp lý.

- Thanh ghi CPU: Quản lý thanh ghi là trách nhiệm của trình biên dịch và hệ điều hành (trong ngữ cảnh chuyển đổi ngữ cảnh). Nó không phải là “quản lý bộ nhớ” theo nghĩa truyền thống, nhưng là một phần của quản lý tài nguyên xử lý.

- Bộ nhớ thứ cấp: Hệ điều hành quản lý việc di chuyển các trang hoặc đoạn bộ nhớ giữa RAM và bộ nhớ thứ cấp (swap space/paging file) trong cơ chế bộ nhớ ảo.

Vậy, mặc dù quản lý bộ nhớ ảnh hưởng gián tiếp đến toàn bộ hệ thống phân cấp, nó tác động trực tiếp và mạnh mẽ nhất đến bộ nhớ chính (RAM) để đảm bảo các chương trình hoạt động hiệu quả.

Câu 2: Ý NGHĨA CỦA VIỆC TỔ CHỨC VÀ QUẢN LÝ BỘ NHỚ TRONG MÁY TÍNH LÀ GÌ?

Trả lời và giải thích chi tiết:

Việc tổ chức và quản lý bộ nhớ là một khía cạnh cực kỳ quan trọng trong thiết kế và vận hành hệ thống máy tính. Ý nghĩa của nó bao gồm nhiều khía cạnh, tác động trực tiếp đến hiệu suất, độ tin cậy và khả năng mở rộng của hệ thống.

- Tối ưu hóa hiệu suất:

- Sử dụng tài nguyên hiệu quả: Bộ nhớ chính (RAM) là một tài nguyên giới hạn và đắt đỏ. Quản lý bộ nhớ giúp phân bổ RAM cho nhiều chương trình cùng lúc, tối đa hóa việc sử dụng CPU bằng cách giảm thời gian CPU phải chờ dữ liệu từ các thiết bị chậm hơn.

- Giảm thời gian truy cập: Bằng cách tổ chức dữ liệu hợp lý, hệ thống có thể giảm thiểu số lần truy cập vào bộ nhớ chậm (như ổ đĩa), tăng tốc độ thực thi chương trình. Các kỹ thuật như bộ nhớ ảo cho phép một chương trình lớn hơn RAM vẫn có thể chạy được.

- Bảo vệ hệ thống và dữ liệu:

- Cách ly tiến trình: Quản lý bộ nhớ đảm bảo rằng mỗi chương trình hoặc tiến trình chỉ có thể truy cập vào vùng bộ nhớ được cấp phát cho nó, ngăn chặn việc một chương trình lỗi hoặc độc hại làm hỏng dữ liệu hoặc mã lệnh của chương trình khác, hoặc của hệ điều hành.

- Phân quyền truy cập: Nó cho phép thiết lập các quyền truy cập khác nhau (đọc, ghi, thực thi) cho các vùng bộ nhớ, tăng cường bảo mật.

- Hỗ trợ đa nhiệm:

- Chạy nhiều chương trình đồng thời: Quản lý bộ nhớ là điều kiện tiên quyết để hệ điều hành có thể chạy nhiều chương trình cùng một lúc. Nó phải chuyển đổi ngữ cảnh giữa các chương trình và cấp phát/thu hồi bộ nhớ linh hoạt.

- Bộ nhớ ảo: Kỹ thuật bộ nhớ ảo cho phép mỗi chương trình nhìn thấy một không gian địa chỉ liên tục và độc lập, ngay cả khi bộ nhớ vật lý bị phân mảnh hoặc nhỏ hơn tổng dung lượng bộ nhớ mà các chương trình yêu cầu. Điều này đơn giản hóa lập trình và cho phép thực thi các ứng dụng lớn.

- Tăng tính linh hoạt và khả năng mở rộng:

- Tái định vị: Các chương trình có thể được nạp vào bất kỳ đâu trong bộ nhớ vật lý mà không cần biên dịch lại, tăng tính linh hoạt.

- Chia sẻ mã/dữ liệu: Cho phép nhiều chương trình chia sẻ cùng một mã hoặc thư viện dữ liệu, tiết kiệm bộ nhớ.

Tóm lại, việc tổ chức và quản lý bộ nhớ là xương sống của một hệ điều hành hiện đại, đảm bảo các chương trình chạy hiệu quả, an toàn và hỗ trợ đa nhiệm mạnh mẽ.

Câu 3: QUẢN LÝ BỘ NHỚ THEO PHÂN ĐOẠN ĐƯỢC THỰC HIỆN NHƯ THẾ NÀO?

Trả lời và giải thích chi tiết:

Quản lý bộ nhớ theo phân đoạn (Segmentation) là một cơ chế quản lý bộ nhớ ảo, trong đó không gian địa chỉ logic của một chương trình được chia thành các đơn vị có kích thước không đều, gọi là các đoạn (segments). Mỗi đoạn thường tương ứng với một đơn vị logic trong chương trình, như một module mã lệnh, một hàm, một khối dữ liệu, ngăn xếp (stack), hoặc vùng heap.

- Tổ chức các đoạn:

- Mỗi chương trình được xem là một tập hợp các đoạn. Mỗi đoạn có một tên (hoặc số hiệu) và một kích thước riêng.

- Địa chỉ logic trong hệ thống phân đoạn bao gồm hai phần: số hiệu đoạn (segment number) và độ lệch trong đoạn (offset).

- Bảng đoạn (Segment Table):

- Mỗi tiến trình có một bảng đoạn riêng. Bảng này lưu trữ thông tin về từng đoạn của tiến trình.

- Mỗi mục nhập trong bảng đoạn chứa:

- Địa chỉ cơ sở (Base Address): Địa chỉ vật lý bắt đầu của đoạn trong bộ nhớ RAM.

- Giới hạn (Limit): Kích thước của đoạn.

- Quyền truy cập (Permissions): Các quyền đọc, ghi, thực thi cho đoạn đó.

- Cơ chế chuyển đổi địa chỉ:

- Khi CPU tạo ra một địa chỉ logic (số hiệu đoạn, độ lệch), hệ thống quản lý bộ nhớ sẽ lấy số hiệu đoạn để tìm đến mục nhập tương ứng trong bảng đoạn của tiến trình hiện tại.

- Hệ thống kiểm tra độ lệch có lớn hơn giới hạn của đoạn không. Nếu có, xảy ra lỗi vi phạm bộ nhớ (segmentation fault).

- Nếu hợp lệ, địa chỉ vật lý được tính bằng cách cộng địa chỉ cơ sở của đoạn với độ lệch:

Địa chỉ vật lý = Base Address + Offset.

- Ưu điểm của phân đoạn:

- Phù hợp với cấu trúc chương trình: Các đoạn tương ứng với các đơn vị logic của chương trình, giúp lập trình viên dễ dàng hơn trong việc quản lý và bảo vệ các phần khác nhau của mã và dữ liệu.

- Bảo vệ bộ nhớ: Dễ dàng áp dụng các quyền truy cập khác nhau cho từng đoạn, tăng cường bảo mật.

- Chia sẻ đoạn: Các tiến trình có thể chia sẻ cùng một đoạn mã hoặc dữ liệu bằng cách trỏ các mục trong bảng đoạn của chúng đến cùng một địa chỉ vật lý của đoạn.

- Nhược điểm:

- Phân mảnh bộ nhớ ngoài: Vì các đoạn có kích thước khác nhau và có thể được nạp/bỏ nạp khỏi bộ nhớ, nó có thể dẫn đến phân mảnh bộ nhớ ngoài (external fragmentation), khiến các khối bộ nhớ trống bị phân tán và không đủ lớn để chứa một đoạn mới, ngay cả khi tổng dung lượng trống đủ.

- Yêu cầu tái định vị động: Các đoạn có thể nằm ở bất kỳ đâu trong bộ nhớ vật lý, đòi hỏi cơ chế tái định vị động để chuyển đổi địa chỉ logic sang vật lý.

Tóm lại, quản lý bộ nhớ theo phân đoạn tổ chức bộ nhớ dựa trên cấu trúc logic của chương trình, sử dụng bảng đoạn để ánh xạ địa chỉ logic sang địa chỉ vật lý và cung cấp các tính năng bảo vệ.

Câu 4: SỰ KHÁC BIỆT TRONG QUẢN LÝ BỘ NHỚ THEO PHÂN TRANG SO VỚI QUẢN LÝ THEO PHÂN ĐOẠN

Trả lời và giải thích chi tiết:

Quản lý bộ nhớ theo phân trang (Paging) và phân đoạn (Segmentation) đều là các cơ chế quản lý bộ nhớ ảo để ánh xạ địa chỉ logic sang địa chỉ vật lý, nhưng chúng có những khác biệt cơ bản về cách tổ chức và mục tiêu:

| Đặc điểm | Phân Trang (Paging) | Phân Đoạn (Segmentation) |

|---|---|---|

| Đơn vị chia | Trang (Page) – kích thước cố định, thường là 4KB, 8KB. | Đoạn (Segment) – kích thước không cố định, tùy thuộc vào cấu trúc logic của chương trình (ví dụ: code, data, stack). |

| Địa chỉ logic | Gồm hai phần: Số trang (Page Number) và Độ lệch trang (Offset). | Gồm hai phần: Số hiệu đoạn (Segment Number) và Độ lệch trong đoạn (Offset). |

| Ánh xạ | Sử dụng Bảng Trang (Page Table) để ánh xạ số trang logic sang khung trang vật lý. | Sử dụng Bảng Đoạn (Segment Table) để ánh xạ số hiệu đoạn logic sang địa chỉ cơ sở vật lý của đoạn. |

| Đối tượng nhìn thấy | Phần cứng (và hệ điều hành) nhìn thấy các trang, lập trình viên thường không nhận biết. | Lập trình viên nhìn thấy các đoạn (ví dụ: vùng code, vùng data, vùng stack) và có thể thao tác với chúng ở cấp độ logic. |

| Phân mảnh | Phân mảnh bộ nhớ trong (Internal Fragmentation): Một phần nhỏ của khung trang cuối cùng có thể không được sử dụng hết. Không có phân mảnh bộ nhớ ngoài. | Phân mảnh bộ nhớ ngoài (External Fragmentation): Các khối bộ nhớ trống bị phân tán, không đủ lớn cho một đoạn mới mặc dù tổng dung lượng trống có đủ. |

| Bảo vệ/Chia sẻ | Bảo vệ và chia sẻ ở cấp độ trang. Khó chia sẻ các cấu trúc dữ liệu logic một cách tự nhiên. | Bảo vệ và chia sẻ ở cấp độ đoạn. Dễ dàng chia sẻ các đoạn logic (ví dụ: các thư viện code) giữa nhiều tiến trình. |

| Tính liên tục | Đảm bảo không gian địa chỉ logic của chương trình là liên tục nhưng các trang vật lý có thể không liên tục. | Các đoạn vật lý có thể không liên tục, nhưng không gian địa chỉ logic trong mỗi đoạn là liên tục. |

| Độ phức tạp | Phức tạp hơn cho phần cứng để quản lý bảng trang lớn. | Phức tạp hơn cho phần mềm để quản lý các đoạn có kích thước biến đổi. |

Tóm lại:

- Phân trang giải quyết vấn đề phân mảnh bộ nhớ ngoài bằng cách chia bộ nhớ thành các khối cố định, nhưng có thể gây phân mảnh bộ nhớ trong. Nó minh bạch với lập trình viên.

- Phân đoạn giải quyết vấn đề tổ chức logic của chương trình, giúp bảo vệ và chia sẻ hiệu quả hơn, nhưng lại đối mặt với phân mảnh bộ nhớ ngoài. Nó rõ ràng hơn với lập trình viên về cấu trúc logic.

Một số hệ thống hiện đại kết hợp cả hai cơ chế này, gọi là phân đoạn kết hợp phân trang (segmented paging) hoặc ngược lại, để tận dụng ưu điểm của cả hai.

Hệ thống và các phương pháp vào ra dữ liệu (Chương 5)

Câu 1: TẠI SAO KHI THỰC HIỆN VÀO/RA (NHẬP/XUẤT) DỮ LIỆU VỚI CÁC THIẾT BỊ NGOẠI VI CỦA MÁY TÍNH PHẢI ÁP DỤNG MỘT TRONG CÁC PHƯƠNG PHÁP VÀO-RA DỮ LIỆU?

Trả lời và giải thích chi tiết:

Việc áp dụng các phương pháp vào-ra (Input/Output – I/O) dữ liệu chuyên biệt khi giao tiếp với các thiết bị ngoại vi là điều cực kỳ cần thiết do sự khác biệt lớn về tốc độ và đặc điểm hoạt động giữa CPU và các thiết bị này.

- Chênh lệch tốc độ: CPU hoạt động ở tốc độ rất cao (GHz), có khả năng thực hiện hàng tỷ lệnh mỗi giây. Ngược lại, các thiết bị ngoại vi như bàn phím, chuột, ổ đĩa, máy in, mạng… hoạt động chậm hơn CPU hàng nghìn, thậm chí hàng triệu lần. Nếu CPU cố gắng giao tiếp trực tiếp với chúng mà không có cơ chế điều phối, CPU sẽ phải dành phần lớn thời gian chờ đợi thiết bị hoàn thành tác vụ, dẫn đến lãng phí tài nguyên xử lý nghiêm trọng và giảm hiệu suất hệ thống.

- Đặc điểm hoạt động đa dạng: Mỗi loại thiết bị ngoại vi có cách thức hoạt động, yêu cầu về dữ liệu và thời gian phản hồi riêng. Ví dụ, bàn phím sinh ra dữ liệu theo sự kiện (khi người dùng gõ phím), máy in cần một luồng dữ liệu liên tục để in, và ổ đĩa cần truy cập theo khối (block).

- Đảm bảo độ tin cậy và chính xác: Các phương pháp I/O giúp đảm bảo rằng dữ liệu được truyền đi và nhận về một cách chính xác, không bị mất mát hay sai lệch do chênh lệch tốc độ hoặc các vấn đề đồng bộ hóa. Chúng cung cấp các cơ chế kiểm tra lỗi, thông báo trạng thái và điều phối luồng dữ liệu.

- Quản lý tài nguyên hiệu quả: Các phương pháp I/O cho phép hệ điều hành quản lý việc truy cập thiết bị ngoại vi, cấp phát tài nguyên cho các tiến trình khác nhau một cách công bằng và hiệu quả, hỗ trợ đa nhiệm.

Các phương pháp I/O phổ biến bao gồm:

- I/O có lập trình (Programmed I/O): CPU liên tục kiểm tra trạng thái của thiết bị.

- I/O theo ngắt (Interrupt-Driven I/O): Thiết bị báo cho CPU khi sẵn sàng bằng cách tạo ra một ngắt.

- Truy cập bộ nhớ trực tiếp (Direct Memory Access – DMA): Thiết bị có thể chuyển dữ liệu trực tiếp đến/từ bộ nhớ mà không cần sự can thiệp liên tục của CPU.

Nhờ có các phương pháp này, CPU có thể tập trung vào các tác vụ tính toán, chỉ tương tác với thiết bị ngoại vi khi cần thiết hoặc khi được thông báo, từ đó tối ưu hóa hiệu suất tổng thể của hệ thống.

Câu 2: CƠ CHẾ ĐỂ ĐƠN VỊ XỬ LÝ TRUNG TÂM BẮT NHỊP ĐƯỢC VỚI HOẠT ĐỘNG CỦA THIẾT BỊ NGOẠI VI Ở PHƯƠNG PHÁP VÀO-RA THEO NGẮT CỨNG LÀ GÌ?

Trả lời và giải thích chi tiết:

Ở phương pháp I/O theo ngắt cứng (Hardware Interrupt-Driven I/O), cơ chế giúp CPU bắt nhịp với các thiết bị ngoại vi dựa vào việc thiết bị tạo ra một “ngắt” (interrupt) để thu hút sự chú ý của CPU, thay vì CPU phải liên tục kiểm tra trạng thái của thiết bị.

- Bộ điều khiển ngắt PIC (Programmable Interrupt Controller): Đây là một chip phần cứng chuyên dụng (ví dụ: Intel 8259 trong kiến trúc PC/AT) có chức năng trung gian giữa các thiết bị ngoại vi và CPU.

- Nhận yêu cầu ngắt (IRQ): Các thiết bị ngoại vi (bàn phím, chuột, ổ đĩa, card mạng…) khi hoàn thành một tác vụ hoặc cần sự chú ý của CPU sẽ gửi một tín hiệu Yêu cầu Ngắt (Interrupt Request – IRQ) đến PIC. Mỗi IRQ được gán cho một đường riêng trên PIC.

- Ưu tiên ngắt: PIC quản lý các yêu cầu ngắt, ưu tiên chúng nếu có nhiều ngắt xảy ra cùng lúc.

- Báo ngắt cho CPU (INT): Khi có một yêu cầu ngắt hợp lệ, PIC sẽ gửi một tín hiệu Báo Ngắt (Interrupt – INT) đến chân ngắt của CPU.

- CPU xử lý ngắt:

- Tạm dừng chương trình hiện tại: Khi CPU nhận tín hiệu INT, nó sẽ tạm dừng việc thực thi chương trình hiện tại ngay sau khi hoàn thành lệnh đang xử lý.

- Gửi tín hiệu INTA (Interrupt Acknowledge): CPU phản hồi lại PIC bằng tín hiệu INTA, báo rằng nó đã sẵn sàng phục vụ ngắt.

- PIC gửi Vector ngắt: PIC nhận INTA và gửi một “số ngắt” (interrupt vector number) hoặc địa chỉ trực tiếp đến CPU. Số ngắt này là một chỉ số vào Bảng vector ngắt (Interrupt Vector Table – IVT) lưu trữ trong bộ nhớ.

- CPU tra cứu IVT: CPU sử dụng số ngắt nhận được để tra cứu trong IVT. IVT chứa các địa chỉ của các chương trình con phục vụ ngắt (Interrupt Service Routine – ISR) tương ứng với từng loại ngắt.

- Lưu trạng thái CPU: Trước khi nhảy đến ISR, CPU sẽ lưu trữ trạng thái hiện tại của nó (ví dụ: các thanh ghi, PC, cờ) vào ngăn xếp (stack) để có thể khôi phục sau này.

- Thực thi ISR: CPU nhảy đến địa chỉ của ISR tương ứng và thực thi mã lệnh trong ISR. ISR là chương trình được viết để xử lý tác vụ cụ thể của thiết bị đã gây ra ngắt.

- Khôi phục trạng thái CPU: Sau khi ISR hoàn thành, CPU khôi phục trạng thái đã lưu từ stack và tiếp tục thực thi chương trình ban đầu từ điểm đã tạm dừng.

Cơ chế này cho phép CPU thực hiện các công việc khác trong khi chờ thiết bị ngoại vi hoàn tất tác vụ, và chỉ phản ứng khi được thiết bị “gọi”, tối ưu hóa hiệu suất tổng thể của hệ thống.

Câu 3: ĐIỀU KIỆN ĐỂ CÓ THỂ THỰC HIỆN VÀO RA DỮ LIỆU THEO PHƯƠNG PHÁP NGẮT CỨNG LÀ GÌ?

Trả lời và giải thích chi tiết:

Để có thể thực hiện vào-ra dữ liệu theo phương pháp ngắt cứng một cách hiệu quả và đáng tin cậy, cần phải thỏa mãn một số điều kiện quan trọng về cả phần cứng và phần mềm:

- Hỗ trợ phần cứng từ CPU: CPU phải có chân ngắt (Interrupt Request pin) và khả năng xử lý ngắt. Điều này bao gồm khả năng lưu trạng thái hiện tại, chuyển đến địa chỉ ISR, và khôi phục trạng thái sau khi ISR hoàn tất.

- Có bộ điều khiển ngắt (PIC) hoặc cơ chế tương đương: Để quản lý các yêu cầu ngắt từ nhiều thiết bị và ưu tiên chúng, một bộ điều khiển ngắt phần cứng là cần thiết. PIC (như 8259) sẽ tập hợp các tín hiệu IRQ, ưu tiên chúng và chuyển một tín hiệu ngắt tổng hợp đến CPU.

- Thiết bị ngoại vi phải có khả năng tạo ngắt: Mỗi thiết bị ngoại vi cần được thiết kế để có thể sinh ra tín hiệu IRQ khi cần (ví dụ: dữ liệu sẵn sàng, lỗi xảy ra, hoàn thành tác vụ).

- Bảng Vector Ngắt (Interrupt Vector Table – IVT) phải được thiết lập: IVT phải được lưu trữ trong bộ nhớ và chứa các địa chỉ chính xác của các Chương trình con phục vụ ngắt (ISR) cho từng loại ngắt. Hệ điều hành hoặc BIOS chịu trách nhiệm thiết lập bảng này.

- Chương trình con phục vụ ngắt (ISR) phải tồn tại và được cài đặt: Đối với mỗi loại ngắt từ một thiết bị cụ thể, phải có một đoạn mã (driver hoặc ISR) được viết để xử lý ngắt đó. Các ISR này phải được nạp vào bộ nhớ và địa chỉ của chúng được cập nhật vào IVT.

- Cờ ngắt (Interrupt Flag – IF) của CPU phải được kích hoạt: CPU có một cờ điều khiển (thường là IF trong thanh ghi EFLAGS/FLAGS) cho phép hoặc không cho phép ngắt. Để ngắt xảy ra, cờ này phải được đặt (enabled). Nếu cờ này bị xóa (disabled), CPU sẽ bỏ qua các tín hiệu ngắt (trừ ngắt không che được – NMI).

- Thiết lập các thanh ghi điều khiển ngắt của thiết bị và PIC: Các thanh ghi trong chip điều khiển thiết bị (ví dụ: IER của UART) và trong PIC (ví dụ: IMR – Interrupt Mask Register) cần được cấu hình đúng để cho phép ngắt mong muốn và che đi các ngắt không mong muốn.

Tóm lại, việc thực hiện ngắt cứng đòi hỏi sự phối hợp chặt chẽ giữa phần cứng CPU, bộ điều khiển ngắt, thiết bị ngoại vi và phần mềm (BIOS/hệ điều hành/driver) để thiết lập và phản ứng đúng đắn với các sự kiện ngắt.

Kiến trúc máy vi tính PC và đơn vị xử lý trung tâm (Chương 6)

Câu 1: ĐƠN VỊ XỬ LÝ TRUNG TÂM KIỂM TRA BIT CỜ NÀO VÀ Ở TIỂU CHU KỲ NÀO TRONG CHU KỲ LỆNH TRƯỚC KHI QUYẾT ĐỊNH THỰC HIỆN HOẶC KHÔNG THỰC HIỆN CHU KỲ NGẮT?

Trả lời và giải thích chi tiết:

Trong chu kỳ thực hiện lệnh của một CPU, quá trình kiểm tra ngắt thường diễn ra ở cuối mỗi chu kỳ lệnh, trước khi bắt đầu chu kỳ tìm nạp lệnh tiếp theo. Đây là thời điểm CPU có thể an toàn xử lý một ngắt mà không làm gián đoạn lệnh đang được thực thi.

- Bit cờ được kiểm tra: CPU kiểm tra cờ ngắt (Interrupt Flag – IF), thường nằm trong thanh ghi EFLAGS (hoặc FLAGS đối với các kiến trúc cũ hơn của Intel 80×86).

- Nếu

IF = 1(ngắt được cho phép), CPU sẽ kiểm tra xem có yêu cầu ngắt nào đang chờ xử lý hay không. - Nếu

IF = 0(ngắt bị cấm), CPU sẽ bỏ qua các yêu cầu ngắt có thể che được (maskable interrupts) và tiếp tục thực thi lệnh tiếp theo trong chương trình.

- Nếu

- Tiểu chu kỳ kiểm tra: Việc kiểm tra cờ ngắt và có yêu cầu ngắt diễn ra ở cuối tiểu chu kỳ thực thi lệnh (Execution Cycle), trước khi CPU bắt đầu tìm nạp lệnh mới. Đây là một bước phụ thêm sau khi một lệnh đã hoàn tất. Nếu có một ngắt đang chờ và IF được kích hoạt, CPU sẽ chuyển sang thực hiện chu kỳ ngắt thay vì chu kỳ tìm nạp lệnh.

Vì vậy, CPU kiểm tra bit cờ IF ở tiểu chu kỳ thực thi lệnh (Execution Cycle), cụ thể là sau khi một lệnh đã hoàn tất thực thi, để quyết định có chuyển sang chu kỳ ngắt hay không.

Câu 2: SỰ KHÁC BIỆT TRONG CÁC THAO TÁC ĐƠN VỊ XỬ LÝ TRUNG TÂM KHI THỰC HIỆN LỆNH GỌI XA (FAR CALL) SO VỚI GỌI GẦN (NEAR CALL) ĐẾN MỘT CHƯƠNG TRÌNH CON ĐÍCH CÓ MỨC ĐẶC QUYỀN THẤP HƠN LÀ GÌ?

Trả lời và giải thích chi tiết:

Trong kiến trúc Intel 80×86 (và các kiến trúc CPU khác), lệnh gọi chương trình con (CALL) có thể là NEAR CALL hoặc FAR CALL, phụ thuộc vào việc chương trình con có nằm trong cùng một đoạn mã (segment) hay không. Sự khác biệt trở nên rõ rệt hơn khi xét đến bảo vệ bộ nhớ và mức đặc quyền.

- Lệnh GỌI GẦN (NEAR CALL):

- Mục đích: Gọi một chương trình con nằm trong cùng một đoạn mã với lệnh CALL hiện tại.

- Thao tác CPU:

- Cất IP vào ngăn xếp: CPU lưu trữ giá trị hiện tại của con trỏ lệnh (IP – Instruction Pointer), tức là địa chỉ offset của lệnh ngay sau CALL, vào ngăn xếp (stack).

- Nạp địa chỉ offset của chương trình con vào IP: CPU nạp địa chỉ offset của chương trình con đích vào IP.

- Thực thi chương trình con: CPU bắt đầu thực thi chương trình con từ địa chỉ mới trong IP.

- Mức đặc quyền: NEAR CALL chỉ liên quan đến offset trong cùng một đoạn, không liên quan đến thay đổi mức đặc quyền. Nó giả định rằng chương trình con có cùng mức đặc quyền với mã gọi.

- Lệnh GỌI XA (FAR CALL):

- Mục đích: Gọi một chương trình con nằm trong một đoạn mã khác. Điều này liên quan đến việc thay đổi cả bộ chọn đoạn (segment selector) và offset.

- Thao tác CPU (khi mức đặc quyền đích BẰNG mức nguồn):

- Cất CS và IP vào ngăn xếp: CPU lưu trữ cả giá trị hiện tại của thanh ghi đoạn mã (CS – Code Segment) và con trỏ lệnh (IP) vào ngăn xếp.

- Nạp bộ chọn đoạn và offset của chương trình con vào CS và IP: CPU nạp bộ chọn đoạn mới vào CS và địa chỉ offset của chương trình con đích vào IP.

- Thực thi chương trình con: CPU bắt đầu thực thi chương trình con ở đoạn mã mới.

- Thao tác CPU (khi mức đặc quyền đích THẤP HƠN mức nguồn): Đây là trường hợp phức tạp hơn và liên quan đến cơ chế bảo vệ của CPU (gọi là “cổng cuộc gọi” – Call Gate).

- Truy cập Cổng cuộc gọi: CPU không trực tiếp nhảy đến đoạn mã đích. Thay vào đó, nó nhảy đến một Cổng cuộc gọi (Call Gate) được định nghĩa trong Bảng mô tả toàn cục (Global Descriptor Table – GDT) hoặc Bảng mô tả cục bộ (Local Descriptor Table – LDT).

- Kiểm tra đặc quyền: Cổng cuộc gọi chứa thông tin về đoạn mã đích và mức đặc quyền của nó. CPU kiểm tra xem mức đặc quyền của tiến trình gọi có đủ để truy cập cổng cuộc gọi và đoạn mã đích hay không.

- Thay đổi ngăn xếp (nếu cần): Nếu mức đặc quyền thay đổi (từ cao hơn xuống thấp hơn), CPU sẽ tự động chuyển sang một ngăn xếp khác, riêng biệt cho mức đặc quyền mới, để bảo vệ dữ liệu của ngăn xếp ở mức đặc quyền cao hơn. Nó sẽ lưu CS, IP, và các tham số vào ngăn xếp mới.

- Nạp bộ chọn đoạn và offset đích: Sau khi kiểm tra thành công, CPU nạp bộ chọn đoạn của chương trình con đích vào CS và offset vào IP.

- Thực thi chương trình con: CPU bắt đầu thực thi chương trình con ở mức đặc quyền thấp hơn.

Điểm khác biệt cốt lõi:

- NEAR CALL: Chỉ thay đổi IP, nằm trong cùng một đoạn mã, không liên quan đến mức đặc quyền.

- FAR CALL (đến mức đặc quyền thấp hơn): Thay đổi cả CS và IP, có thể thay đổi ngăn xếp, và quan trọng nhất là trải qua quá trình kiểm tra bảo vệ và chuyển đổi ngữ cảnh ngăn xếp thông qua Call Gate để đảm bảo tính toàn vẹn và bảo mật của hệ thống.

Các thiết bị vào ra dữ liệu và giao diện vào ra dữ liệu chuẩn (Chương 8)

Câu 1: DỰA TRÊN CƠ SỞ NÀO MÀ TỪ SỐ NGẮT ĐƠN VỊ XỬ LÝ TRUNG TÂM XÁC ĐỊNH ĐƯỢC ĐỊA CHỈ CỦA CHƯƠNG TRÌNH CON PHỤC VỤ NGẮT?

Trả lời và giải thích chi tiết:

Khi một ngắt xảy ra và CPU nhận được “số ngắt” (interrupt vector number) từ Bộ điều khiển ngắt lập trình được (PIC), nó sử dụng số ngắt này làm chỉ mục để truy cập vào Bảng Vector Ngắt (Interrupt Vector Table – IVT). Đây là cơ sở để CPU xác định địa chỉ của Chương trình con phục vụ ngắt (Interrupt Service Routine – ISR) tương ứng.

- Bảng Vector Ngắt (IVT):

- IVT là một cấu trúc dữ liệu đặc biệt, thường nằm ở một vùng bộ nhớ cố định (ví dụ: ở đầu bộ nhớ RAM vật lý trong kiến trúc 80×86).

- Mỗi mục nhập trong IVT (còn gọi là “vector ngắt” hoặc “con trỏ ngắt”) là một cặp địa chỉ (segment:offset) hoặc một địa chỉ 32/64 bit trỏ đến vị trí bộ nhớ nơi ISR bắt đầu.

- Mỗi số ngắt được gán cho một ISR cụ thể. Ví dụ, số ngắt 9 có thể dành cho bàn phím, số ngắt 14 cho ổ đĩa cứng, v.v.

- Quá trình xác định địa chỉ ISR:

- PIC gửi số ngắt: Khi một thiết bị ngoại vi tạo ra IRQ, PIC sẽ nhận và xử lý nó. Sau khi CPU xác nhận ngắt (qua INTA), PIC sẽ gửi số ngắt tương ứng (ví dụ: 08H cho timer, 09H cho bàn phím) đến CPU.

- CPU sử dụng số ngắt làm chỉ mục: CPU nhận số ngắt này và nhân nó với kích thước của một vector ngắt (ví dụ: 4 byte cho địa chỉ 20-bit trong real mode của x86, hoặc 8 byte cho địa chỉ 32/64-bit trong protected mode). Kết quả là địa chỉ trong IVT của mục nhập chứa địa chỉ ISR.

- Đọc địa chỉ ISR từ IVT: CPU đọc địa chỉ (segment:offset hoặc địa chỉ phẳng) từ vị trí đã tính trong IVT.

- Nhảy đến ISR: CPU nạp địa chỉ này vào thanh ghi CS (segment) và IP (offset) (hoặc EIP/RIP trong chế độ bảo vệ) và bắt đầu thực thi ISR.

Do đó, IVT đóng vai trò như một bản đồ, cho phép CPU nhanh chóng tìm thấy và nhảy đến mã xử lý ngắt phù hợp dựa trên số ngắt nhận được.

Câu 2: TRONG CƠ CHẾ PHỤC VỤ NGẮT CỨNG, BỘ ĐIỀU KHIỂN NGẮT PIC CÓ KHẢ NĂNG NHẬN CÙNG MỘT LÚC BAO NHIÊU TÍN HIỆU BÁO NGẮT?

Trả lời và giải thích chi tiết:

Trong các máy tính PC thế hệ cũ (như PC/XT, PC/AT) và vẫn là nền tảng cơ bản cho các hệ thống hiện đại, hệ thống ngắt cứng được xây dựng trên cơ sở các chip Bộ điều khiển ngắt lập trình được (PIC) dòng Intel 8259A.

- Một chip 8259A: Một chip PIC 8259A có khả năng nhận 8 tín hiệu yêu cầu ngắt riêng biệt, được đánh số từ IRQ0 đến IRQ7.

- Hệ thống PC/AT điển hình: Để hỗ trợ nhiều thiết bị ngoại vi hơn, kiến trúc PC/AT sử dụng hai chip PIC 8259A được kết nối cascade (thác).

- Chip PIC chính (Master PIC) được nối trực tiếp với CPU và nhận 8 tín hiệu IRQ.

- Chip PIC thứ cấp (Slave PIC) được nối với một trong các đường IRQ của Master PIC (thường là IRQ2 hoặc IRQ9 trên các hệ thống hiện đại). Chip Slave này cũng nhận 8 tín hiệu IRQ của riêng nó.

- Tổng cộng, một hệ thống PC/AT với hai PIC có thể xử lý 15 tín hiệu yêu cầu ngắt (IRQ0 đến IRQ15, với IRQ2/9 được dùng để nối Slave PIC).

Vì vậy, một chip PIC 8259A có thể nhận 8 tín hiệu báo ngắt. Trong một hệ thống PC điển hình với hai chip PIC, tổng số đường IRQ khả dụng là 15.

Câu 3: HỆ THỐNG NGẮT CỨNG TRÊN MÁY TÍNH PC ĐƯỢC XÁC LẬP CHẾ ĐỘ KẾT THÚC NGẮT BÌNH THƯỜNG EOI, VÌ VẬY TRONG CHƯƠNG TRÌNH PHỤC VỤ NGẮT CẦN PHẢI CÓ LỆNH GÌ PHÁT ĐẾN PIC ĐỂ BÁO KẾT THÚC NGẮT?

Trả lời và giải thích chi tiết:

Trong cơ chế ngắt cứng của kiến trúc PC, sau khi một Chương trình con phục vụ ngắt (ISR) hoàn tất việc xử lý, CPU cần thông báo cho Bộ điều khiển ngắt lập trình được (PIC) rằng ngắt đã được xử lý xong. Điều này đặc biệt quan trọng khi PIC được cấu hình ở chế độ Kết thúc Ngắt Bình thường (End Of Interrupt – EOI).

- Mục đích của EOI: Khi một ngắt xảy ra, PIC sẽ giữ bit ISR (In-Service Register) tương ứng với ngắt đó ở trạng thái “đang phục vụ”. Nếu PIC không nhận được tín hiệu EOI, nó sẽ cho rằng ngắt đó vẫn đang được xử lý và sẽ không chấp nhận hoặc ưu tiên các ngắt khác trên cùng đường IRQ hoặc các ngắt có mức ưu tiên thấp hơn. Điều này có thể dẫn đến hệ thống bị kẹt hoặc mất ngắt.

- Lệnh cần phát: Để báo hiệu kết thúc ngắt trong chế độ EOI, CPU (thông qua phần mềm trong ISR) phải gửi một lệnh điều khiển EOI đến PIC. Cụ thể, đây là một lệnh ghi vào một cổng I/O của PIC.

- Trong kiến trúc x86, lệnh này thường được thực hiện bằng cách ghi giá trị EOI (ví dụ:

20H) vào cổng điều khiển lệnh của PIC (20Hcho Master PIC hoặcA0Hcho Slave PIC). - Ví dụ:

OUT 20H, 20H(cho Master PIC) là một cách để gửi tín hiệu EOI.

- Trong kiến trúc x86, lệnh này thường được thực hiện bằng cách ghi giá trị EOI (ví dụ:

- Hậu quả nếu không có EOI: Nếu không có lệnh EOI được gửi, bit ISR tương ứng trong PIC sẽ không được xóa, và PIC sẽ không thể xử lý các ngắt tiếp theo đúng cách.

Vì vậy, để đảm bảo hoạt động đúng đắn của hệ thống ngắt, trong chương trình phục vụ ngắt (ISR), cần phải có lệnh gửi tín hiệu EOI đến PIC để báo hiệu rằng ngắt đã hoàn tất xử lý.

Câu 4: ĐIỀU KIỆN ĐỂ THIẾT BỊ UART THỰC HIỆN ĐƯỢC CHỨC NĂNG TRUYỀN DỮ LIỆU KIỂU NỐI TIẾP KHÔNG ĐỒNG BỘ LÀ GÌ?

Trả lời và giải thích chi tiết:

Thiết bị UART (Universal Asynchronous Receiver/Transmitter), ví dụ như chip 8250 hoặc các phiên bản kế nhiệm, là một thành phần quan trọng cho việc truyền dữ liệu nối tiếp không đồng bộ. Để UART có thể thực hiện chức năng này, cần có một số điều kiện và cấu hình cụ thể:

- Cấu hình tốc độ Baud (Baud Rate): Cả bên gửi và bên nhận phải được cấu hình để hoạt động ở cùng một tốc độ Baud (số lượng bit được truyền mỗi giây). Tốc độ Baud được thiết lập thông qua thanh ghi bộ chia Baud Rate Generator (BRG) trong UART.

- Cấu hình định dạng khung dữ liệu (Frame Format): Cả hai bên cũng phải đồng ý về cấu trúc của mỗi “khung” dữ liệu được truyền. Định dạng khung bao gồm:

- Số bit dữ liệu: Thường là 5, 6, 7 hoặc 8 bit.

- Bit chẵn lẻ (Parity Bit): Có thể là chẵn (Even), lẻ (Odd), không có (None), hoặc luôn 0/1 (Mark/Space). Bit này dùng để kiểm tra lỗi đơn giản.

- Số bit dừng (Stop Bits): Thường là 1, 1.5 hoặc 2 bit, dùng để đánh dấu kết thúc của một khung dữ liệu.

- Bit khởi động (Start Bit): Luôn có một bit khởi động (giá trị 0) để báo hiệu bắt đầu một khung dữ liệu.

Các thiết lập này được cấu hình trong Thanh ghi Điều khiển Đường truyền (Line Control Register – LCR) của UART.

- Đường truyền vật lý: Phải có một kết nối vật lý hoạt động giữa hai thiết bị (ví dụ: cáp RS-232, USB-to-serial converter) để các tín hiệu điện có thể truyền qua.

- UART phải được cấp nguồn và hoạt động: Chip UART phải được cấp nguồn đúng cách và các mạch logic bên trong phải hoạt động bình thường.

- Cho phép ngắt (nếu sử dụng I/O theo ngắt): Nếu UART được sử dụng theo phương pháp I/O ngắt, các ngắt tương ứng trong Thanh ghi Cho phép Ngắt (Interrupt Enable Register – IER) của UART và trong PIC phải được kích hoạt.

Tóm lại, điều kiện cơ bản để UART thực hiện chức năng truyền dữ liệu nối tiếp không đồng bộ là cả hai bên truyền và nhận phải được cấu hình với cùng các tham số về tốc độ Baud và định dạng khung dữ liệu, đồng thời có kết nối vật lý hoạt động.

Câu 5: KHI THỰC HIỆN PHÁT DỮ LIỆU THEO PHƯƠNG PHÁP THĂM DÒ QUA THIẾT BỊ UART, CẦN TRUY CẬP THANH GHI NÀO TRONG THIẾT BỊ UART ĐỂ KIỂM TRA VÀ XÁC ĐỊNH ĐƯỢC TRẠNG THÁI THIẾT BỊ UART SẴN SÀNG PHÁT ĐI MỘT BYTE DỮ LIỆU MỚI?

Trả lời và giải thích chi tiết:

Khi thực hiện phát dữ liệu theo phương pháp thăm dò (Polling I/O) qua UART, CPU cần liên tục kiểm tra trạng thái của UART để biết khi nào nó sẵn sàng nhận thêm dữ liệu để phát. Thanh ghi được sử dụng cho mục đích này là Thanh ghi Trạng thái Đường truyền (Line Status Register – LSR).

- Thanh ghi LSR: Chứa các bit cờ phản ánh trạng thái hiện tại của đường truyền dữ liệu và các bộ đệm bên trong UART.

- Bit quan trọng để phát dữ liệu: Để xác định UART đã sẵn sàng phát đi một byte dữ liệu mới, CPU cần kiểm tra bit THRE (Transmitter Holding Register Empty) trong LSR.

- Nếu

THRE = 1: Bộ đệm giữ dữ liệu phát (Transmitter Holding Register – THR) đang trống, nghĩa là UART đã gửi xong byte dữ liệu trước đó và sẵn sàng nhận byte mới từ CPU để đưa vào THR. - Nếu

THRE = 0: THR đang chứa dữ liệu chờ phát hoặc đang trong quá trình phát, và CPU không nên ghi thêm dữ liệu vào THR lúc này để tránh làm mất dữ liệu.

- Nếu

Quá trình phát dữ liệu bằng thăm dò:

- CPU muốn gửi một byte dữ liệu.

- CPU đọc nội dung của thanh ghi LSR.

- CPU kiểm tra bit THRE của LSR.

- Nếu THRE = 0, CPU lặp lại bước 2 và 3 (chờ đợi).

- Nếu THRE = 1, CPU ghi byte dữ liệu cần phát vào Thanh ghi dữ liệu phát (Transmitter Holding Register – THR).

- UART sẽ tự động lấy dữ liệu từ THR và chuyển đổi nó thành tín hiệu nối tiếp để phát đi.

Do đó, để kiểm tra trạng thái sẵn sàng phát dữ liệu, CPU cần truy cập và kiểm tra bit THRE trong Thanh ghi Trạng thái Đường truyền (LSR).

Câu 6: ĐỂ CÓ THỂ THỰC HIỆN TRUYỀN DỮ LIỆU THEO PHƯƠNG PHÁP NGẮT QUA THIẾT BỊ UART, CẦN TRUY CẬP CÁC THANH GHI NÀO SAU ĐÂY TRONG THIẾT BỊ UART ĐỂ XÁC LẬP BỔ XUNG CHẾ ĐỘ TRUYỀN (PHÁT/NHẬN) DỮ LIỆU THEO PHƯƠNG PHÁP NGẮT?

Trả lời và giải thích chi tiết:

Để cấu hình UART hoạt động theo phương pháp truyền dữ liệu theo ngắt, CPU cần truy cập và cấu hình một số thanh ghi quan trọng trong UART để kích hoạt các loại ngắt cụ thể. Các thanh ghi chính bao gồm:

- Thanh ghi Cho phép Ngắt (Interrupt Enable Register – IER): Đây là thanh ghi quan trọng nhất để kích hoạt các ngắt của UART. CPU ghi các bit vào IER để cho phép các loại ngắt sau:

- Ngắt khi bộ đệm nhận đầy dữ liệu (Receiver Data Available Interrupt).

- Ngắt khi bộ đệm phát trống (Transmitter Holding Register Empty Interrupt).

- Ngắt khi có lỗi trên đường truyền (Line Status Interrupt).

- Ngắt khi có thay đổi trạng thái modem (Modem Status Interrupt).

Khi một bit trong IER được đặt, UART sẽ tạo ra một IRQ nếu sự kiện ngắt tương ứng xảy ra.

- Thanh ghi Điều khiển Đường truyền (Line Control Register – LCR): Mặc dù chủ yếu dùng để cấu hình định dạng khung dữ liệu (bit dữ liệu, parity, bit dừng), LCR cũng có thể chứa một bit cho phép truy cập vào các thanh ghi bộ chia tốc độ Baud (DLAB – Divisor Latch Access Bit). Việc cấu hình tốc độ Baud là cần thiết cho mọi phương pháp truyền dữ liệu, kể cả ngắt.

- Thanh ghi Điều khiển Modem (Modem Control Register – MCR): MCR được sử dụng để điều khiển các tín hiệu bắt tay với modem. Quan trọng hơn, nó chứa một bit (OUT2 hoặc Auxiliary Output 2) có thể được sử dụng để cho phép ngắt của UART đi đến bộ điều khiển ngắt PIC. Nếu bit này không được kích hoạt, các ngắt từ UART sẽ bị chặn trước khi đến PIC.

- Thanh ghi Nhận dạng Nguồn Ngắt (Interrupt Identification Register – IIR): Mặc dù không dùng để xác lập chế độ ngắt, IIR rất quan trọng trong ISR để nhận dạng loại ngắt nào đã xảy ra. CPU đọc IIR để biết sự kiện ngắt nào đã khiến UART tạo ra IRQ, từ đó thực thi phần mã phù hợp trong ISR.

Do đó, các thanh ghi chính cần truy cập để xác lập bổ sung chế độ truyền dữ liệu theo phương pháp ngắt là IER, LCR (để thiết lập DLAB và tốc độ Baud), và MCR (để cho phép ngắt đi đến PIC). IIR là để đọc thông tin về ngắt, không phải để cấu hình.

Thiết bị vào ra cơ bản (Chương 9)

Câu 1: CHỨC NĂNG CỦA THIẾT BỊ BÀN PHÍM MÁY TÍNH LÀ GÌ?

Trả lời và giải thích chi tiết:

Bàn phím máy tính là một trong những thiết bị ngoại vi cơ bản và quan trọng nhất, đóng vai trò là giao diện nhập liệu chính giữa người dùng và máy tính. Chức năng cốt lõi của bàn phím bao gồm:

- Chuyển đổi tác động vật lý thành tín hiệu điện tử: Khi người dùng nhấn một phím, một công tắc điện tử dưới phím đó sẽ đóng hoặc mở. Bàn phím có một bộ vi điều khiển (microcontroller) tích hợp quét ma trận các phím để phát hiện sự thay đổi trạng thái này.

- Tạo mã quét (Scan Code): Thay vì gửi trực tiếp ký tự ASCII, bộ vi điều khiển của bàn phím sẽ tạo ra một mã duy nhất gọi là “mã quét” (scan code) cho mỗi lần phím được nhấn (make code) và nhả (break code). Mã quét này là một số nguyên đại diện cho vị trí vật lý của phím trên bàn phím, không phụ thuộc vào ký tự mà phím đó biểu diễn (ví dụ: phím ‘A’ có cùng mã quét dù đang ở chế độ chữ hoa hay chữ thường, hay được gán thành một phím chức năng khác).

- Gửi mã quét đến máy tính: Mã quét này sau đó được gửi đến máy tính thông qua một giao thức nối tiếp (ví dụ: PS/2, USB).

- Phát hiện và xử lý tổ hợp phím: Bàn phím cũng có khả năng phát hiện các tổ hợp phím (ví dụ: Shift + A, Ctrl + C) và gửi các mã quét tương ứng hoặc một chuỗi mã quét để máy tính xử lý.

- Hỗ trợ các chức năng đặc biệt: Nhiều bàn phím hiện đại còn có các phím đa phương tiện, phím chức năng lập trình được, giúp tăng cường trải nghiệm người dùng.

Tóm lại, chức năng chính của bàn phím là chuyển đổi hành động nhấn/nhả phím của người dùng thành các mã quét điện tử và truyền các mã này đến máy tính để hệ điều hành và các ứng dụng có thể giải thích và phản hồi.

Câu 2: CƠ CHẾ NÀO ĐƯỢC SỬ DỤNG TRONG ĐIỀU PHỐI SỬ DỤNG ĐƯỜNG TRUYỀN DỮ LIỆU GIỮA THIẾT BỊ GIAO DIỆN BÀN PHÍM VÀ THIẾT BỊ BÀN PHÍM (KEYBOARD)?

Trả lời và giải thích chi tiết:

Cơ chế điều phối sử dụng đường truyền dữ liệu giữa thiết bị bàn phím (keyboard) và thiết bị giao diện bàn phím (keyboard controller trên bo mạch chủ của máy tính) thường là theo kiểu “chủ-tớ” (Master-Slave) hoặc “thiết bị phát động” (Initiator-Target). Trong bối cảnh PC, bàn phím hoạt động như một thiết bị “tớ” và bộ điều khiển bàn phím (thường là một phần của chip Super I/O hoặc tích hợp vào chipset hiện đại) trên bo mạch chủ là “chủ”.

- Cơ chế hoạt động:

- Bàn phím là thiết bị tớ (Slave): Bàn phím không tự ý gửi dữ liệu liên tục. Thay vào đó, nó đợi lệnh từ bộ điều khiển bàn phím.

- Bộ điều khiển bàn phím là thiết bị chủ (Master): Bộ điều khiển bàn phím khởi xướng các giao tiếp với bàn phím.

- Truyền dữ liệu theo sự kiện (Event-driven): Khi một phím được nhấn hoặc nhả, bộ vi điều khiển trong bàn phím sẽ tạo ra mã quét. Nó lưu trữ mã này trong bộ đệm nội bộ và sau đó tạo ra một tín hiệu ngắt (IRQ) (hoặc một tín hiệu sẵn sàng dữ liệu) gửi đến bộ điều khiển bàn phím trên bo mạch chủ.

- Bộ điều khiển bàn phím đọc dữ liệu: Khi bộ điều khiển bàn phím nhận được tín hiệu từ bàn phím (thường là qua đường ngắt IRQ1), nó sẽ phát ra một lệnh đến bàn phím để đọc mã quét từ bộ đệm của bàn phím. Dữ liệu được truyền qua giao thức nối tiếp đồng bộ (PS/2) hoặc nối tiếp USB.

- Tạo ngắt cho CPU: Sau khi bộ điều khiển bàn phím đọc thành công mã quét, nó sẽ tạo ra một ngắt IRQ1 cho CPU để thông báo rằng có dữ liệu bàn phím mới sẵn sàng trong bộ đệm của bộ điều khiển.

- Giao tiếp nối tiếp đồng bộ: Dù hoạt động của người dùng là không đồng bộ, nhưng bản thân giao tiếp giữa bàn phím và bộ điều khiển bàn phím (đặc biệt qua cổng PS/2) lại là nối tiếp đồng bộ. Tức là, có một đường dữ liệu và một đường đồng hồ. Bàn phím sẽ gửi dữ liệu bit theo từng nhịp đồng hồ, do bộ điều khiển bàn phím (hoặc bản thân bàn phím) tạo ra. Điều này đảm bảo tính toàn vẹn và đồng bộ hóa ở cấp độ bit.

Vậy, cơ chế điều phối là kiểu “chủ-tớ” (bộ điều khiển là chủ, bàn phím là tớ), và giao tiếp vật lý thường là nối tiếp đồng bộ (đối với PS/2), hoạt động theo phương pháp ngắt để báo hiệu dữ liệu sẵn sàng.

Câu 3: HÀM HỆ THỐNG ĐỌC THIẾT BỊ GIAO DIỆN BÀN PHÍM ĐƯỢC KÍCH HOẠT THEO PHƯƠNG PHÁP NÀO?

Trả lời và giải thích chi tiết:

Hàm hệ thống đọc thiết bị giao diện bàn phím (tức là hàm trong BIOS hoặc hệ điều hành để đọc dữ liệu từ bộ điều khiển bàn phím) chủ yếu được kích hoạt theo phương pháp ngắt (Interrupt-Driven I/O).

- Quy trình chi tiết:

- Người dùng nhấn một phím.

- Bàn phím gửi mã quét đến bộ điều khiển bàn phím.

- Bộ điều khiển bàn phím đọc mã quét và lưu vào bộ đệm nội bộ của nó.

- Bộ điều khiển bàn phím tạo ra một tín hiệu ngắt (IRQ1) và gửi đến Bộ điều khiển ngắt lập trình được (PIC).

- PIC chuyển tín hiệu ngắt này đến CPU.

- CPU tạm dừng công việc hiện tại và nhảy đến Chương trình con phục vụ ngắt (ISR) cho ngắt bàn phím (vector ngắt thường là 9 trong kiến trúc x86).

- Trong ISR của bàn phím, hàm hệ thống sẽ được gọi để:

- Đọc mã quét từ cổng dữ liệu của bộ điều khiển bàn phím (ví dụ: cổng 60h).

- Chuyển đổi mã quét thành ký tự ASCII hoặc ký tự mở rộng (extend key code), có tính đến trạng thái của các phím Shift, Ctrl, Alt, Caps Lock…

- Lưu trữ ký tự đã chuyển đổi vào một bộ đệm vòng (circular buffer) của hệ điều hành.

- Gửi tín hiệu EOI (End Of Interrupt) đến PIC để thông báo ngắt đã được xử lý.

- CPU tiếp tục công việc ban đầu.

- Lợi ích của phương pháp ngắt:

- Hiệu quả: CPU không phải liên tục “thăm dò” (polling) bộ điều khiển bàn phím, tiết kiệm tài nguyên xử lý.

- Phản ứng nhanh: Hệ thống phản ứng ngay lập tức khi có sự kiện nhập liệu từ bàn phím.

- Hỗ trợ đa nhiệm: Cho phép CPU thực hiện các tác vụ khác trong khi chờ đợi người dùng nhập liệu.

Trong một số trường hợp đặc biệt (ví dụ: trong giai đoạn khởi động BIOS ban đầu hoặc khi có lỗi nghiêm trọng), có thể sử dụng thăm dò, nhưng đây không phải là phương pháp chính thức để đọc bàn phím trong hệ điều hành đang hoạt động bình thường.

Vì vậy, hàm hệ thống đọc thiết bị giao diện bàn phím được kích hoạt chủ yếu theo phương pháp ngắt cứng.

Câu 4: KIỂU DÁNG KÝ TỰ HIỂN THỊ TRÊN MÀN HÌNH ĐƯỢC XÁC ĐỊNH BỞI KHỐI CHỨC NĂNG NÀO?

Trả lời và giải thích chi tiết:

Kiểu dáng ký tự hiển thị trên màn hình được xác định bởi sự phối hợp của nhiều khối chức năng, nhưng thành phần trực tiếp chịu trách nhiệm chuyển đổi mã ký tự thành hình ảnh hiển thị là Bộ điều khiển đồ họa (Graphics Controller) hay Bộ điều khiển hiển thị (Display Controller) và cụ thể hơn là Bộ tạo ký tự (Character Generator) bên trong nó (hoặc trong bộ nhớ video).

- Quá trình hiển thị ký tự:

- CPU gửi mã ký tự: Khi CPU hoặc phần mềm muốn hiển thị một ký tự (ví dụ: ‘A’), nó sẽ gửi mã ASCII hoặc mã tương ứng của ký tự đó đến bộ nhớ hiển thị (video memory hay frame buffer) của card đồ họa.

- Bộ điều khiển đồ họa xử lý: Bộ điều khiển đồ họa liên tục đọc nội dung của bộ nhớ hiển thị.

- Bộ tạo ký tự (Character Generator): Đây là một phần quan trọng trong bộ điều khiển đồ họa (hoặc một ROM/RAM đặc biệt trên card đồ họa chứa các mẫu font chữ). Khi bộ điều khiển đọc một mã ký tự từ bộ nhớ hiển thị, nó sẽ sử dụng mã này làm chỉ mục để tra cứu trong bộ tạo ký tự. Bộ tạo ký tự sẽ trả về một mẫu bit (pixel pattern) tương ứng với hình dạng của ký tự đó.

- Chuyển đổi thành tín hiệu video: Các mẫu bit này sau đó được chuyển đổi thành tín hiệu video (analog hoặc digital) và gửi đến màn hình.

- Mẫu font chữ: Các mẫu font chữ (ví dụ: font 8×8 pixel) được lưu trữ dưới dạng bitmap trong ROM của card đồ họa hoặc có thể là trong RAM video (đặc biệt đối với các hệ thống đồ họa hiện đại hơn cho phép font chữ tùy chỉnh và đa dạng).

Vậy, kiểu dáng ký tự hiển thị trên màn hình được xác định bởi Bộ điều khiển đồ họa (Graphics Controller), thông qua chức năng của Bộ tạo ký tự (Character Generator) và các mẫu font chữ được lưu trữ.

Tổ chức thông tin trên đĩa từ (Chương 10)

Câu 1: ĐƠN VỊ LƯU TRỮ NHỎ NHẤT ĐƯỢC HỆ ĐIỀU HÀNH SỬ DỤNG ĐỂ LƯU TRỮ VÀ QUẢN LÝ VIỆC LƯU TRỮ TẬP TIN TRÊN Ổ ĐĨA CỨNG LÀ GÌ?

Trả lời và giải thích chi tiết:

Trong các hệ thống quản lý tập tin (File System) như FAT (File Allocation Table) hay NTFS (New Technology File System), đơn vị lưu trữ nhỏ nhất mà hệ điều hành sử dụng để phân bổ không gian cho các tập tin trên ổ đĩa cứng không phải là byte hay sector, mà là Liên cung (Cluster).

- Sector: Là đơn vị vật lý nhỏ nhất trên ổ đĩa cứng mà phần cứng có thể đọc hoặc ghi. Kích thước sector thường là 512 byte hoặc 4KB.

- Cluster (Liên cung): Là một nhóm các sector liền kề. Kích thước của một cluster có thể là 1 sector (512 byte hoặc 4KB), 2 sector, 4 sector, 8 sector, hoặc lớn hơn, thường là một lũy thừa của 2. Hệ điều hành quản lý việc phân bổ không gian đĩa ở cấp độ cluster chứ không phải cấp độ sector.

Lý do sử dụng Cluster:

- Giảm gánh nặng quản lý: Nếu hệ điều hành quản lý từng sector riêng lẻ, số lượng các mục nhập cần theo dõi sẽ rất lớn, làm tăng kích thước của bảng phân bổ tập tin và làm chậm hoạt động. Bằng cách nhóm các sector thành cluster lớn hơn, số lượng các đơn vị cần quản lý giảm đáng kể.

- Hiệu quả lưu trữ: Giúp tăng hiệu suất truy cập đĩa vì các file lớn có thể được đọc/ghi trong các khối lớn hơn.

- Phân mảnh nội bộ (Internal Fragmentation): Mặc dù cluster giúp quản lý hiệu quả, nhưng nó có thể gây ra phân mảnh nội bộ. Nghĩa là, nếu một tập tin có kích thước không phải là bội số của kích thước cluster, phần cuối của cluster cuối cùng được cấp phát cho tập tin đó sẽ không được sử dụng hết, nhưng vẫn được coi là “chiếm dụng” bởi tập tin.

Vì vậy, đơn vị lưu trữ nhỏ nhất được hệ điều hành sử dụng để cấp phát và quản lý không gian đĩa cho tập tin là Liên cung (Cluster).

Câu 2: CUNG KHỞI ĐỘNG CHỦ MBR CÓ CHỨC NĂNG GÌ VÀ ĐƯỢC TỔ CHỨC NHƯ THẾ NÀO?

Trả lời và giải thích chi tiết:

Cung khởi động chủ (Master Boot Record – MBR) là một cấu trúc dữ liệu quan trọng nằm ở sector đầu tiên (sector 0) của ổ đĩa cứng. Nó đóng vai trò trung tâm trong quá trình khởi động máy tính.

- Chức năng của MBR:

- Chứa mã khởi động (Boot Loader Code): MBR chứa một chương trình nhỏ gọi là boot loader code (hoặc Master Boot Code). Nhiệm vụ chính của mã này là quét Bảng phân vùng để tìm phân vùng hoạt động (active partition) hoặc phân vùng khởi động.

- Chứa Bảng phân vùng (Partition Table): MBR chứa một bảng thông tin về tất cả các phân vùng chính (primary partitions) và phân vùng mở rộng (extended partition) trên ổ đĩa. Bảng này định nghĩa vị trí bắt đầu và kết thúc của mỗi phân vùng, kích thước và loại của chúng. MBR truyền quyền điều khiển cho phân vùng được đánh dấu là “hoạt động”.

- Chứa Chữ ký đĩa (Disk Signature): Một giá trị duy nhất 4 byte dùng để nhận dạng ổ đĩa.

- Tổ chức của MBR:

MBR thường có kích thước 512 byte và được tổ chức như sau:- 446 byte đầu tiên: Chứa mã khởi động (Master Boot Code). Đoạn mã này thực hiện các bước ban đầu của quá trình khởi động, chủ yếu là tìm kiếm và chuyển quyền điều khiển cho boot sector của phân vùng hoạt động.

- 64 byte tiếp theo: Chứa Bảng phân vùng (Partition Table). Bảng này có thể chứa tối đa 4 mục nhập, mỗi mục dài 16 byte, mô tả một phân vùng chính trên ổ đĩa.

- 2 byte cuối cùng (byte 510 và 511): Chứa chữ ký khởi động (Boot Signature) là

AA55H. Đây là một giá trị ma thuật mà BIOS kiểm tra để xác định xem sector này có phải là một MBR hợp lệ hay không. Nếu không tìm thấy chữ ký này, BIOS sẽ không cố gắng khởi động từ ổ đĩa đó.

Quá trình khởi động với MBR:

- BIOS của máy tính đọc MBR từ sector 0 của ổ đĩa cứng.

- BIOS kiểm tra chữ ký

AA55Hở cuối MBR. - Nếu hợp lệ, BIOS chuyển quyền điều khiển cho mã khởi động trong MBR.

- Mã khởi động trong MBR quét Bảng phân vùng để tìm phân vùng hoạt động.

- Khi tìm thấy phân vùng hoạt động, mã khởi động MBR sẽ đọc boot sector của phân vùng đó (Volume Boot Record – VBR) và chuyển quyền điều khiển cho mã khởi động trong VBR.

- VBR sau đó sẽ tiếp tục quá trình khởi động bằng cách nạp hệ điều hành.

MBR là một thành phần kế thừa từ kiến trúc PC ban đầu và vẫn được sử dụng rộng rãi, mặc dù các hệ thống UEFI hiện đại đã chuyển sang sử dụng Bảng phân vùng GUID (GPT – GUID Partition Table) thay thế.

Câu 3: Ở HỆ THỐNG QUẢN LÝ TẬP TIN FAT, VỊ TRÍ CÁC NƠI CHỨA MỘT TẬP TIN TRONG VOLUME ĐƯỢC XÁC ĐỊNH NHƯ THẾ NÀO?

Trả lời và giải thích chi tiết:

Trong hệ thống quản lý tập tin FAT (File Allocation Table – Bảng phân bổ tập tin), vị trí các nơi chứa một tập tin trên ổ đĩa (trong một volume) được xác định thông qua sự kết hợp của mục nhập thư mục (Directory Entry) và chính Bảng phân bổ tập tin (FAT).

- Cấu trúc Volume FAT: Một volume FAT có cấu trúc cơ bản bao gồm:

- Boot Sector: Chứa thông tin về volume (kích thước sector, cluster, số FAT…).

- Vùng FAT (FAT Region): Chứa một hoặc nhiều bản sao của Bảng phân bổ tập tin. Đây là nơi mấu chốt để theo dõi vị trí các cluster của tập tin.

- Vùng Thư mục gốc (Root Directory Region): (Chỉ có trong FAT12/16) Chứa các mục nhập cho các tập tin và thư mục ở cấp cao nhất.

- Vùng dữ liệu (Data Region): Là nơi lưu trữ thực tế nội dung của các tập tin và thư mục con. Vùng này được chia thành các cluster.

- Xác định vị trí tập tin:

- Mục nhập thư mục (Directory Entry): Khi bạn tìm kiếm một tập tin, hệ điều hành sẽ tìm mục nhập tương ứng của nó trong thư mục chứa. Mỗi mục nhập thư mục của tập tin chứa các thông tin như tên tập tin, kích thước, ngày giờ tạo/sửa đổi, và quan trọng nhất là cluster bắt đầu (Starting Cluster) của tập tin.

- Bảng phân bổ tập tin (FAT):

- Bảng FAT là một mảng các mục nhập, mỗi mục tương ứng với một cluster trong vùng dữ liệu.

- Giá trị trong mỗi mục nhập FAT sẽ trỏ đến cluster tiếp theo trong chuỗi các cluster tạo nên tập tin.

- Nếu giá trị là

0000h, cluster đó trống. - Nếu giá trị là

FFF7h(hoặc tương tự), cluster đó bị đánh dấu là hỏng. - Nếu giá trị là

FFF8h(hoặc tương tự), cluster đó là cluster cuối cùng của một tập tin.

Quá trình đọc tập tin:

Để đọc một tập tin, hệ điều hành sẽ:

- Đọc mục nhập thư mục của tập tin để lấy cluster bắt đầu.

- Sử dụng cluster bắt đầu này làm chỉ mục để tra cứu trong Bảng FAT, tìm ra cluster tiếp theo.

- Tiếp tục tra cứu trong Bảng FAT cho đến khi gặp mục nhập báo hiệu cluster cuối cùng của tập tin.

- Bằng cách này, hệ điều hành có thể xây dựng một danh sách các cluster (thường không liên tục) tạo nên tập tin và đọc nội dung từ các cluster đó trong vùng dữ liệu.

Cơ chế này cho phép các tập tin bị phân mảnh (lưu trữ ở các cluster không liền kề) nhưng vẫn có thể được truy cập một cách logic. Đây là cách mà các bài tập kiến trúc máy tính về hệ thống file thường được đặt ra.

Câu 4: CÁC TẬP TIN CÓ KÍCH THƯỚC LỚN HƠN 4 GBYTE CÓ THỂ ĐƯỢC QUẢN LÝ BỞI HỆ THỐNG TẬP TIN NÀO?

Trả lời và giải thích chi tiết:

Câu hỏi này liên quan đến giới hạn kích thước tập tin và volume của các hệ thống tập tin khác nhau.

- Hệ thống tập tin FAT (File Allocation Table):

- FAT16: Có giới hạn kích thước tập tin tối đa là 2 GB (hoặc 4 GB với một số cấu hình cluster đặc biệt). Kích thước volume tối đa là 2 GB.

- FAT32: Cải thiện đáng kể so với FAT16. Với FAT32, kích thước tập tin tối đa là 4 GB (chính xác là 4,294,967,295 bytes – 1 byte dưới 4 GB). Kích thước volume tối đa lên đến 2 TB (terabyte) hoặc 16 TB tùy theo kích thước sector.

Vì vậy, FAT32 không thể quản lý các tập tin có kích thước lớn hơn 4 GB. Các tập tin như file ảnh đĩa lớn, video 4K chất lượng cao thường vượt quá giới hạn này.

- Hệ thống tập tin NTFS (New Technology File System):

- NTFS là hệ thống tập tin tiêu chuẩn cho các hệ điều hành Windows hiện đại (từ Windows NT trở đi) và được thiết kế với khả năng mở rộng rất cao.

- Kích thước tập tin tối đa: Về lý thuyết, NTFS có thể hỗ trợ tập tin có kích thước lên tới 16 EB (exabyte) – 1KB, tức là lớn hơn 4 GB rất nhiều. Trong thực tế, giới hạn thường là do hệ điều hành hoặc phần cứng.